The 3-D lattice formulation is a logical extension of the 2-D Burg algorithm and, analogously, a set of 3-D reflection coefficients  $\{\rho(n,m,u)\}$  can be derived. Again, the reflection coefficients are calculated directly from the input data samples. This method is basically a 3-D AR model fitting algorithm.

This algorithm is essentially a 3-D Burg algorithm which given an optimal MMSE estimate for stationary processes when the image extent is much greater than the extent of the filter H.  $(z_1, z_2, z_3)$ . Signal flow diagrams for the 3-D FIR and IIR prediction filters are similar to 2-D lattice filters with additional delay elements.

### D. Results

The most significant results to arising out of these investigations can be summarized as follows:

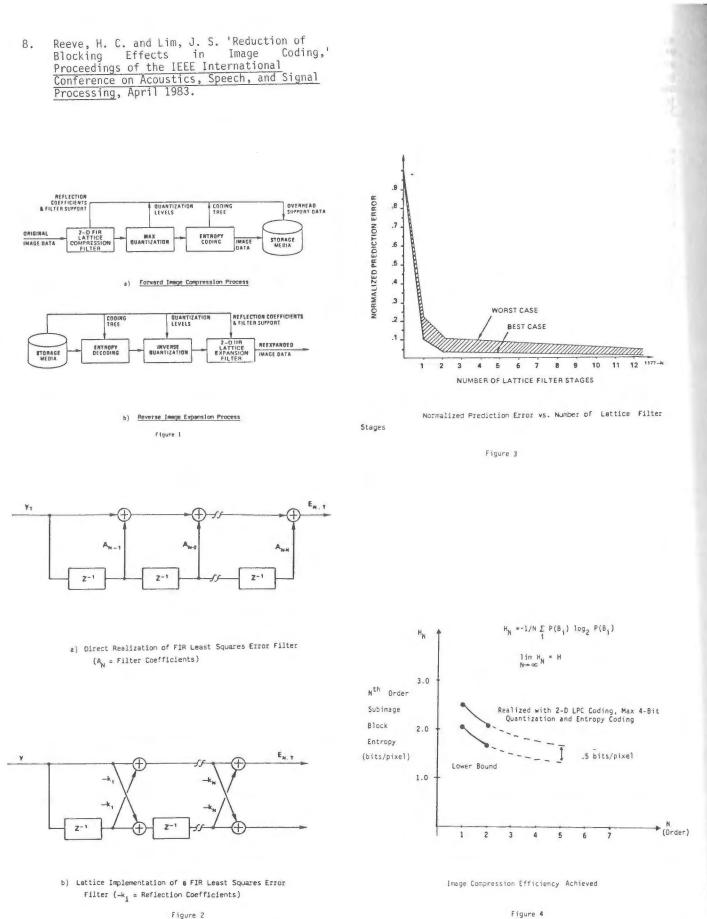

1) <u>Reflection Coefficients</u> - Calculated by the harmonic mean method are extremely good means of characterizing 2-D imagery data in a MMSE sense. As demonstrated experimentally herein, very low residual errors remain after only a few stages of lattice filtering.

2) Experimentally Verified - That the 2-D Burg algorithm as implemented here with appropriate support can be used for imagery compression purposes in the spatial domain. Heretofore, no 2-D LPC imagery coding of this nature had been investigated. This paper described a valuable new spatial compression technique. It is <u>suitable for real-time</u> <u>applications</u> yielding impressive (50-90 percent) image compression factors with, in most cases, imperceptible image fidelity deterioration. When 2-D LPC-induced distortion occurs, it can be removed by simple image enhancement type filtering techniques.<sup>8</sup>

3) A New 2-D In-Place Method - For real-time computation of the 2-D lattice filter coefficients and subsequent imagery data filtering has been derived and verified experimentally with actual imagery data. This method provides intermediate results at any filter stage and is amenable to multidimensional MMSE digital filtering in excess This new method of in-place lattice of 2-D. forward and reverse filtering was utilized for display of intermediate imagery results display after each stage of the 2-D LPC process. With this algorithm, it is possible to form 'imagery' composed from only selected stages of residuals. In other words, imagery from which selected nearest-neighbor pixel correlations have been removed can be generated. This methodology is, in effect, capable of selective decoupling, in a MMSE sense, multivariate function variables. This behavior is afforded by to the Gram-Schmidt orthogonalization realized by the lattice filter structure itself.

4) Extension of 2-D LPC Techniques - To 3-D demonstrating that with the appropriate ordering of multidimensional digital signal points into 'past' and 'future', the resulting LPC filters retain the same stability and analytical properties attributed to 2-D and experimentally demonstrated herein. These 2-D lattice filter designs can readily be extended to N dimensions, as well as to n stages in each dimension. The prediction error results for each dimension can be independently obtained and the final prediction

value calculated as a root-sum-square composite. This methodology can be utilized effectively to realize a multivariate function analysis MMSE prediction capability.

As a result of these investigations, several areas remain prime candidates for further work. These areas include:

<u>2-D Filter Stability</u> - To include additional algorithms for both forward and backward prediction.

backward prediction. New and Automated 2-D Filter Design <u>Methods</u> - Investigations of the performance of reflection coefficient determination algorithms in addition to the 2-D Burg algorithm harmonic-mean method.

3) Determination of a Quantitative Fidelity Criterion - More representative of imagery utility.

4) <u>Development of Precise Methods</u> - Imagery testing, evaluation, and performance verification.

5) <u>Utilization of Evolving State-of-the-Art</u>

5) Utilization of Evolving State-of-the-Art Hardware - Laser disks, VHSIC/VLSI integration, memories, CPU interfaces, etc.

6) Practical Extension of these LPC Methodscorrelation, experimental behavior, and adaptive prediction in a MMSE sense. This 2-D formalism is also suitable for analysis of other 2-D or multi-dimensional stochastic processes.

7) Comparison with the Discrete Cosine Transform (DCT) - 2-D data compression applications via a suitable quantitative measure.

The above candidate research areas all constitute promising topics for future work. The full benefit of MMSE LPC analysis is applicable to other than just the multidimensional digital data compression problem.

### References

- Harlick, R. and Klein, R. 'A Study of Adaptive Image Compression Techniques,' <u>University of Kansas</u>, AD-A094678.

- Marzetta, T. L. 'A Linear Prediction Approach to Two-Dimensional Spectral Factorization and Spectral Estimation,' <u>Ph.D. Dissertation</u> Massachusetts Institute of Technology, 1978.

- Poehler, P.L. 'Data Compression of Imagery Using Linear Predictive Coding Techniques,' <u>Ph.D. Dissertation</u>, Florida Institute of Technology, 1983.

- Parker, S. R. and Kayran, A. H. 'Lattice Parameter Autoregressive Modeling of Two-Dimensional Fields,' submitted to the <u>IEEE</u> <u>Transactions on Acoustics, Speech, and Signal</u> <u>Processing, May, 1983.</u>

- 5. Chen, T. C. and DeFigueiredo, R. J. P. 'An Image Transform Coding Scheme Based on Spatial Domain Consideration,' <u>IEEE</u> <u>Transactions on Pattern Analysis and Machine</u> <u>Intelligence</u>, Vol. PAM I-5, No.3, May 1983.

- Makhoul, J. 'Stable and Efficient Methods for Linear Prediction,' <u>IEEE Transactions on</u> <u>Acoustics, Speech, and Signal Processing</u>, <u>October</u>, 1977.

- Max, J. 'Quantizing for Minimum Distortion,' <u>IRE Transactions on Information Theory</u>, Vol. <u>IT-6</u>, pp 7-12, March 1960.

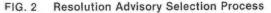

Figure 2

### A TERRAIN DATA/DIGITAL MAP SYSTEM FOR LHX

G. O. Burnham, C. Benning, R. Rivard

Texas Instruments Incorporated P.O. Box 405, M/S 3407 Lewisville, Texas 75067

### Abstract

The Light Helicopter (LHX) is a new aerial platform designed to perform vertical lift missions for Army aviation in the air/land battle of 1995 and beyond. This paper briefly describes the avionics functions required to support LHX missions, including mission management and digital map data retrieval. Presented are some preliminary ideas on terrain data system functions and a discussion of how implementing these functions in the LHX integrated architecture would impact the overall avionics suite.

### Overview

The Air/Land Battle 2000 concept employs Army aviation in whole or in part in all mission areas and battlefield tasks. Army aviation must rapidly deploy and engage enemy forces; conduct reconnaissance and airmobile and logistic operations; and provide C<sup>3</sup>I, airborne fire direction, intelligence and electronic warfare operations, and battlefield interdiction. The threat is real, both quantitatively and qualitatively. In facing this projected enemy threat the Army Aviation Mission Area (AAMA) analysis identified many deficiencies in their current aircraft fleet, including aging and obsolescent aircraft that cannot be upgraded satisfactorily to meet tactical challenges. The Light Helicopter (LHX) family is envisioned as the Army aircraft that will overcome this. It is a new aerial platform designed to perform vertical lift missions for Army aviation in the air/land battle of 1995 and beyond. Depending on mission requirements and cost-effectiveness analyses, it may or may not be a multiple-version aircraft. If more than one version (e.g., scout attack and utility/ observation) evolves, all versions will employ many common subsystems such as engines, rotors, drive trains, and core avionics.

Avionic processing equipment has been traditionally designed for specific subsystems in which it was intended to operate. This approach has led to different architectures, hardware, and software support within the same system. Providing a low-cost, sustainable, mission-effective avionics system requires fault-tolerant, modular processing architecture and processing modules. Essential in this development is the timely and cost-effective insertion of very-high-speed integrated circuit (VHSIC) technology. With full-scale engineering development of LHX scheduled for FY86, it is imperative to initiate development of a VHSIC-based avionics architecture to ensure feasibility of an avionics system capable of meeting the processing requirements dictated by the missions and functions of LHX and to avoid early obsolescence or costly retrofitting.

One of the functions to be implemented into the LHX avionics is a terrain data system capable of working in conjunction with the navigation system to provide accurate terrain correlation navigation updates as well as various displays critical to low-level NOE flights.

### LHX System

Table 1 lists the avionics functions required to support LHX missions. The LHX processing architecture has been defined to provide the signal and data processing necessary to implement these functional subsystems. The processing which they require, coupled with stringent physical constraints of an advanced rotorcraft, dictate an integrated architecture approach that crosses functional boundaries to permit the sharing of processing resources. The processing architecture implements the sensor fusion algorithms that combine the data of multiple subsystems to create a highly synergistic system; however, the control structure also

| Function                         | Preprocessing<br>(MOPS) | Array Processing<br>(MOPS) | Data Processing<br>(MIPS) | Program Memory<br>(KWDS) | Data Memory<br>(MBITS) |

|----------------------------------|-------------------------|----------------------------|---------------------------|--------------------------|------------------------|

| Target acquisition               | 978                     | 125                        | 20                        | 150                      | 33                     |

| Fire control                     | _                       | -                          | 0.75                      | 139                      | 1.5                    |

| Aircraft survivability equipment | 70                      | 2                          | 5                         | 40                       | 0.2                    |

| Terrain data                     | _                       | 343                        | 7.5                       | 120                      | 81                     |

| Navigation                       | _                       | 10                         | 9                         | 96                       | 4                      |

| Communication                    | _                       | 138                        | 3.5                       | 127                      | 4                      |

| Mission management               |                         | 0                          | 24                        | 148                      | 27                     |

| Flight control (3)               | -                       | 0                          | 2.3                       | 48                       | -                      |

| Total                            | 1,048                   | 618                        | 72                        | 868                      | 151                    |

TABLE 1. LHX PROCESSING REQUIREMENTS

Copyright © American Institute of Aeronautics and

Astronautics, Inc., 1984. All rights reserved.

allows autonomous operation of the subsystems while maintaining deterministic processing time lines.

Table 1 also presents estimates of the required program memory, data memory, and processing. Three types of processing are required: complex vector, real array, and scalar. Five processing modules have been defined: complex vector processing module, array processing module, data processing module, memory module, and mission computer executive moddule.

### LHX Mission Management Subsystem

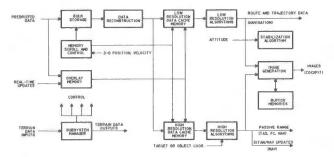

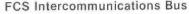

The objective of the mission management subsystem is to integrate and coordinate all activities within the overall system. These components, Figure 1, include a central manager, data base manager, display manager, and subsystem manager for each subsystem. It should be understood that the functions of the central manager, data base manager, and display manager are distributed among the various subsystems.

|                                            | CONTROL CONT                               | FUNCTION                     | HARDWARE                 |

|--------------------------------------------|--------------------------------------------|------------------------------|--------------------------|

| DISPLAY<br>MANAGER                         | TARGET<br>ACQUISITION<br>MANAGER<br>MAINTE | TARGET ACQUISITION           | SENSORS                  |

| PILDT                                      | COMMUNICATION                              | CONNUNICATION                | CONFUNICATION            |

|                                            | FIRE CONTROL<br>MANAGER                    | FIRE CONTROL<br>ALGORITHMS   | WEAPONS                  |

|                                            | NAVIGATION NAMAGER                         | NAVIGATION<br>ALGORITHMS     | SENSORS                  |

| SYSTEM<br>RE-BRIEF<br>HECKOUT<br>REPORTING | TERRAIN DATA                               | TERRAIN DATA<br>ALGORITHHS   | DIGITAL MAP<br>DATA BASE |

| SYSTEM<br>TA BASE<br>IANAGER               | SURVIVABILITY<br>MANAGER                   | SURVIVABILITY<br>ALGORITHINS |                          |

Figure 1. Mission Management Functions

The central manager manages the various high-level functions of the system, e.g., those that are common to all subsystems or those that either involve more than one subsystem or take more than a few seconds to perform or require interaction with the pilot. The central manager must maintain models of the system's configuration, the overall mission, and the status of the various aircraft systems. These models primarily provide the pilot with a summary and tentative evaluation of the current situation. The central manager interacts with the pilot to refine its internal models and to plan appropriate activities (route planning, tactic selection, weapon handoff, etc.). It also inter-acts with the subsystem managers to optimize resource allocation, execute pilot requests or planned activities, and coordinate sensor assignments. At the same time, the central manager must monitor the status of the various subsystems, perform inflight testing/reconfiguration, log all mission activities, and handle routine situations. It is the central manager's duty to process pilot inputs (voice commands, keyboard entries, etc.) appropriately and to integrate the output of subsystem data (video displays and speech output). When doing this, the central manager tries to predict the pilot's current information needs and to provide suitable default inputs. Often, when several tasks are to be performed, the central manager

prioritizes and sequences them, including any setup, follow-up, or subtasks. This is particularly important when some of the tasks must be performed by the pilot.

The data base manager maintains a shared central data base. The subsystems initiate requests for the storage or retrieval of certain data. The data base manager then transforms all references to actual memory addresses and performs the necessary data base functions. Since there will be various types of memory storage in the system (perhaps with different access times, word lengths, error correction or detection capability, EMP protection, power backup, etc.), the data base manager decides before and during the mission where and how data shall be stored to optimally meet mission requirements. It also performs any automatic or periodic data functions on its own.

The display manager meets the changing information needs of the pilot. As different subsystems produce information to be displayed, the display manager must decide the best way to make this information available to the pilot, taking into conside-ration the data's priority. Choices include merging the new data with the data currently being displayed, overwriting part of the display, waiting until the pilot finishes with the current task before interrupting, letting the pilot know that the data is available but will not be displayed until requested, or using an attention-getting device such as color, high-intensity or flashing graphics, audible tone, or spoken phrase. The display manager must keep track of what the pilot is currently viewing as well as what he has just viewed. Using this information and a description of the current situation, the display manager predicts what the pilot will want to see next, labels the programmable keys appropriately, and starts computing the highest probability displays to minimize the processing time required once the pilot makes a choice.

Certain functions are common to all subsystem managers. Each must keep the central manager informed of any changes in the subsystem's status, mode, or configuration. In addition to the shared data base managed by the data base manager, each subsystem will also have local memory storage for its own use. Each subsystem manager is responsible for controlling access to its local storage and any data transfer to or from the shared system data base or other subsystems. To a large extent, fault monitoring and inflight testing will be performed at the subsystem level by each subsystem manager. While the final decision on sensor assignments and reassignments is made by the central manager, each subsystem manager generates requests for the sensors it needs and controls the sensors it has already been assigned. In addition, certain data areas, processors, sensors, or equipment may be dedicated to a specific subsystem manager. What procedures to call and what parameters to call with them are decided at the subsystem level. If a procedure needs to communicate with another subsystem, with the central manager or pilot, or with the system data base, the subsystem manager is responsible for constructing an appropriate symbolic request and addressing it to the central manager, data base manager, display manager, or the desired subsystem manager.

The target acquisition subsystem manager's functions also include determining the area to be searched with the subsystem's sensors, localing targets (azimuth and elevation), identifying and classifying targets (using data from other subsystems, digital terrain maps, prebriefed data, the pilot, and external sources), and maintaining the current target list.

The communications subsystem manager maintains and uses prebriefed frequency and call sign data; controls the message conditioning functions; manages target handoff, radio navigation, and IFF communications; is responsible for distributing the system's data to the outside world; and routes incoming data (such as inflight updates).

The fire control subsystem manager is the primary weapon manager. When using certain weapons, it determines what maneuvers are required to properly align the aircraft before launch. It contributes recommendations for weapon and platform assignments and processes target designations and fire commands. When target data is sent or received via communications, this subsystem is responsible for the message content.

The navigation subsystem manager maintains status and control of the Kalman filters and controls and updates the state vectors. It calculates the optimal trajectory to follow, taking into account the automatic flight and obstacle avoidance algorithms. It is in charge of the passive ranging and the offboard or non-line-of-sight target cueing functions. It controls the primary vehicle reference system and manages coordinate transformations.

The terrain data subsystem manager maintains the aircraft's current position relative to the digital map data base during all maneuvers. It resolves about line-of-sight conditions. It must handle regeneration of the appropriate map resolution from the compressed data, combine map data with any overlay data, and provide smooth map scrolling through the data base for both calculations and display functions. This manager fine-tunes route plans to take maximum advantage of the terrain. During internal or external updates or temporary loss of external navigation data, this system selects and orients the digital map from prominent local terrain features to maintain the aircraft's position at all times.

The survivability subsystem manager constantly monitors and categorizes threats, maintains the current threat list, warns the pilot of any threats, recommends and sets up appropriate maneuvers and countermeasures, and initiates any automatic or requested countermeasures or threat surveillance.

In summary, the pilot communicates with the system via the central manager. The central manager coordinates (sets priorities, resolves conflicts, assigns modes, etc.) the interactions between the subsystem managers. The data manager supports symbolic data access and maintains the system data base. Each subsystem manager controls all activity internal to its own subsystem, including management of any assigned sensors or memory storage, processing, testing, and reconfiguration.

### Terrain Data Subsystem (TDS)

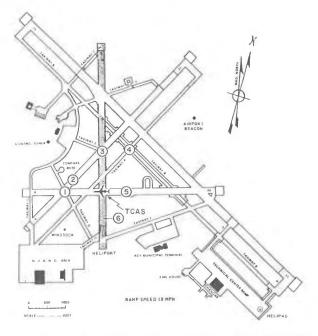

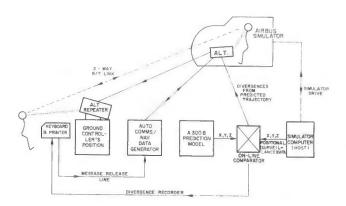

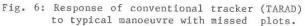

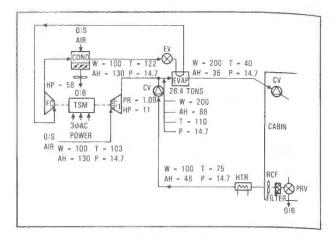

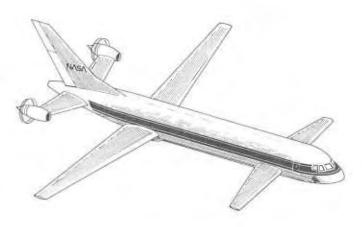

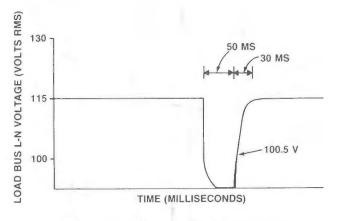

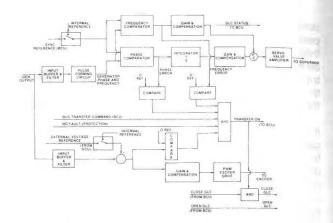

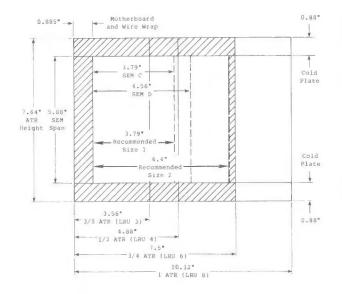

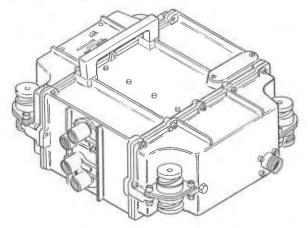

The TDS is a digital map data retrieval system that conditions stored digital map data into a form useful for avionics system algorithms. Modern avionics systems use digital data to perform terrain correlation navigation functions (e.g., SITAN) and to aid in TF/TA schemes, mission planning, and visual presentation of stored terrain information. An LHX TDS must provide digital imagery to allow the crew to quickly orient itself georgraphically, determine and display threat envelopes as a function of aircraft position, calculate and display the optimum flight path between two geographic points, automate mission planning, and allow precise prepointing of targeting sensors by supplying 3-D relative position between aircraft and prestored or mission-acquired targets. Figure 2 presents an example of functional flow.

Terrain data processing includes three major sections: data retrieval, processing algorithms, and display formatting. Data retrieval involves the control and interfacing of the bulk/cache memory section. The processing algorithms contain the functional algorithms associated with a terrain data system (e.g., SITAN or passive ranging). Display formatting the data produces information in the correct form to be displayed.

Figure 2. Terrain Data Functional Flow

The referenced map data is stored in a compressed format in a nonvolatile bulk memory system that contains terrain features, elevations, threat information, and cultural data. This information will come from the Defense Mapping Agency (DMA) and intelligence missions. The resolution of this data defines the accuracy of the system; therefore, system error is a determining factor in the selection of the data compression scheme.

Data accessed from the bulk memory undergoes data reconstruction (the inverse of the data compression algorithm) and is stored in small, fast-access time cache memories. These cache memories are large enough to allow for platform dynamics between refreshes; i.e., the storage area of these memories is based on the flight dynamics of the helicopter. The memory scroll and control function scrolls data into the cache memories when needed and provides the overall control for the retrieval system. Scrolling is dependent on vehicle speed and attitude. Real-time updates of terrain, cultural, and threat data acquired during the mission are needed. This information may be received either offboard or onboard and is stored in an update memory that is addressed and scrolled into the cache memories in a fashion similar to that of the bulk system.

High- and low-resolution data algorithms are performed after data retrieval. Passive ranging of targets from the TAS inputs is an example of a high-resolution algorithm. The TAS provides FLIRderived target azimuth and elevation information to the terrain data subsystem, allowing the terrain system to trace a line-of-sight radial through the map data to determine target range and the local slope of the terrain at the target. The target range is determined by the intersection of a ray from the platform, defined by azimuth and elevation to the target, with the terrain along the line-ofsight vector. The local slope is useful in many target identification algorithms. In an active radar mode, the TAS could provide target azimuth and range to the terrain system, which would then give local slope and target elevation.

High-resolution data is needed when creating realistic digital imagery. A perspective image of encountered terrain requires three steps: radial addressing, hidden-line computations, and scene generation. Radials of sight defined by display resolution, field of view, and sight distance are addressed in the cache memories. The elevations of the radial samples are scaled with respect to distance from the observation point and compared to see which points are hidden. A projection of the points not hidden is used to generate the scene to be displayed. A plan view image is created by displaying the elevations, features, and/or cultural data from a rectangularly addressed array of points about a reference observation point. Other examples of high-resolution algorithms are data conditioning for SITAN updates and data overlay of display images.

An example of a low-resolution data algorithm is a route-planning algorithm that uses stored threats, targets, terrain, and cultural data with a coarse mission route and mission parameters to plan optimal mission routes. These routes will take into account terrain variations and the line of sight of the identified threats. Given the start and end points of a mission, approved waypoints (points between start and end that are safe to travel) are determined and all possible routes through these points plotted. Deterministic rules are then used to pick the optimal route, with mission-acquired information being used to update and change the route when necessary.

The display formatting function converts the processed data into a display format. Examples are the overlaying of threat and target information onto scenes and perspective radial combinations in which all radials in the field of view are combined and filtered to create a pleasing scene. A stabilization algorithm is required to take roll and pitch into account in image displays.

TABLE 2. LHX TERRAIN DATA SYSTEM REQUIREMENTS PRELIMINARY

- AREA COVERAGE

- DATA SOURCE

- I/O

- .

- I/O DATA QUALITY

DISPLAY

- NAVIGATION

- TF/TA

- DISPLAY MODES (256 × 256 PIXELS)

- PLAN VIEW

- LINE-OF-SIGHT

- PERSPECTIVE VIEW (OPTIONAL)

- AIRCRAFT VELOCITY

- DISPLAY UPDATE RATES

- FRAME

- COMPLETE SCENE

- SIZE, WEIGHT, POWER

450 KNOTS

ELEVATION

60 FRAMES/SECOND 10 TO 30 SECONDS 1.5 ATR, 45 POUNDS, 450 WATTS

100 KM × 100 KM, EXPANDABLE TO

ELEVATION DATA TO TF/TA, NAV,

WEAPON DELIVERY, THREAT AVOIDANCE

1,000 KM BY 1,000 KM DMA LEVEL 1

I DISPLAY LEVEL MSE

100 METER CEP FOR SITAN NO UNDERESTIMATES OF TERRAIN

Baseline Requirements. Table 2 summarizes the base-Tine requirements for the TDS. It can be seen that the minimum area to be covered is 100 km x 100 km expandable to larger coverage by adding more memory or by exchanging memory modules. The source data will consist of DMA Level-I Digital Terrain Elevation Data (DTED), Digital Feature Analysis Data (DFA), plus imagery and information from other sources such as Landsat and intelligence sources. The TDS data will be distributed in a raw or preprocessed form; for example, information sent to the TF/TA processor could be an array of elevation values and/or vertical obstructions and heights, or range and angle information required to generate TF/TA commands.

Because of the large data storage requirements, some form of data compression will be required to minimize memory requirements. For this purpose, techniques are suitable, e.g., discrete cosine transforms, Block Truncation Coding. Hadamard transforms, and polynomial surface coding. Texas Instruments is conducting studies as part of the Air Forces Integrated Terrain Access and Retrieval System (ITARS) program to determine the impact of data compression reconstruction techniques and the performance of TF/TA, navigation, display, threat avoidance and weapon delivery algorithms on system hardware and software implementation. As a result of the studies, it will be possible to match the data compression technique to the application and select the optimal implementation. Examples of criteria for selecting data compression/reconstruction algorithms appear in Table 2 under the heading I/O data quality. The TDS will be able to provide plan views and direct line-of-sight views and be capable of generating real-time perspective views if required.

Present design goals are to have a TDS that will operate for aircraft velocities up to 450 knots,

display at 60 frames/second and have favorable size, weight, and power characteristics as shown in Table 2.

Again, it must be stated that Table 2 represents a baseline set of requirements which will evolve as new technology and new user requirements are identified and defined.

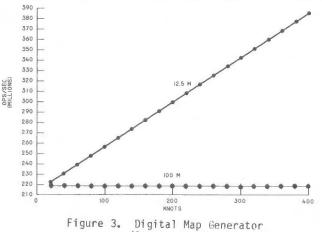

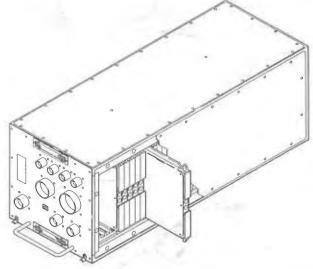

Terrain Data Subsystem Implementation Issues. Several areas inherent in the defined TDS require innovative design to allow implementation of the subsystem within the physical constraints of LHX. The bulk memory must be nonvolatile and lightweight and have reasonable access times. The leading technologies in this area are bubble memories and mediumdensity magnetic-tape technology. Data compression techniques currently in use may need to be improved to reduce the required storage to a more manageable level. Real-time generation of digital imagery requires very-high-speed address and graphics generation. This task seems to be ideally suited for VHSIC processors. Two architectures currently being used for terrain processing are the (DMG) and the alternative DMG.

The DMG which was developed under contract with the U.S. Army Avionics Research and Development activity, reconstructs compressed digital map information and provides outputs suitable for driving a CRT display. The DMG has three major sections: block-oriented functions, per-frame functions, and video processor functions. Initally, functions are performed on blocks of data. The magnetic-tape loader (MTL) stores 81 Universal Transverse Mercator (UTM) blocks of digital terrain data. Each UTM block represents 12.5 x 12.5 kilometers. The intermediate memory acts as a cache memory, feeding data to the elevation and cultural reconstruction processors.

Elevation data is reconstructed with a Discrete Cosine Transform/Differential Pulse Code Modulation method. A footprint method is used to reconstruct cultural features. Reconstructed data is then stored in the scene memory, which acts as another cache memory, feeding data to the per-frame functions. Functions are then performed each display

(Operations Per Second)

## TABLE 3. DMG THROUGHPUT REQUIREMENTS (DMG Operations per Second (12.5 meter data)

300 Knots

| Tasks                    | Adds     | Lookup   | Compares | Logical     | Shift    | Mults    |  |

|--------------------------|----------|----------|----------|-------------|----------|----------|--|

| Elevation reconstruction | 3.60E+07 | 6.83E+03 | 1.02E+04 | 6.83E+03    | 2.71E+05 | 3.55E+07 |  |

| Feature reconstruct      | 4.35E+06 | 3.47E+03 | 1.12E+04 | 1.69E+02    | 1.74E+04 |          |  |

| Per-frame tasks          | 6.29E+07 |          | 5.60E+07 | 2.45E+07    |          | 3.50E+06 |  |

| Totals                   | 9.93E+07 | 1.03E+04 | 5.60E+07 | 2.45E+07    | 2.08E+05 | 3.90E+07 |  |

| Tasks                    | Sin-Cos  | Inv Tan  | Divides  | Square Root | Ex Add   | Ex Mult  |  |

| Elevation reconstruction | 3.54E+07 |          |          |             |          |          |  |

| Feature reconstruct      |          |          |          |             |          |          |  |

| Per-frame tasks          | 6.00E+05 | 6.00E+01 | 6.00E+01 | 6.00E+01    | 7.00E+06 | 3.50E+06 |  |

| Totals                   | 4.23E+07 | 6.00E+01 | 6.00E+01 | 6.00E+01    | 7.00E+06 | 3.50E+06 |  |

|                          |          |          |          |             |          |          |  |

Total OPS/second3.43E+06Total memory46 MBITS

#### DMG Operations per Second (100 meter data) 300 Knots

| Tasks                    | Adds     | Lookup   | Compares | Logical     | Shift    | Mults    |  |

|--------------------------|----------|----------|----------|-------------|----------|----------|--|

| Elevation reconstruction | 1.37E+05 | 1.09E+03 | 2.99E+03 | 1.99E+03    | 2.01E+03 | 1.30E+05 |  |

| Feature reconstruct      | 1.27E+05 | 1.01E+03 | 3.26E+03 | 4.94E+01    | 5.06E+03 |          |  |

| Per-frame tasks          | 6.29E+07 |          | 5.60E+07 | 2.45E+07    |          | 3.50E+06 |  |

| Totals                   | 6.32E+07 | 3.00E+03 | 5.60E+07 | 2.45E+07    | 7.06E+03 | 3.63E+06 |  |

| Tasks                    | Sin-Cos  | Inv Tan  | Divides  | Square Root | Ex Add   | Ex Mult  |  |

| Elevation reconstruction | 1.30E+05 |          |          |             |          |          |  |

| Feature reconstruct      |          |          |          |             |          |          |  |

| Per-frame tasks          | 6.00E+06 | 6.00E+01 | 6.00E+01 | 6.00E+01    | 7.00E+06 | 3.50E+06 |  |

| Totals                   | 7.03E+06 | 6.00E+01 | 6.00E+01 | 6.00E+01    | 7.00E+06 | 3.50E+06 |  |

|                          |          |          |          |             |          |          |  |

Total OPS/second2.15E+08Total memory46 MBITS

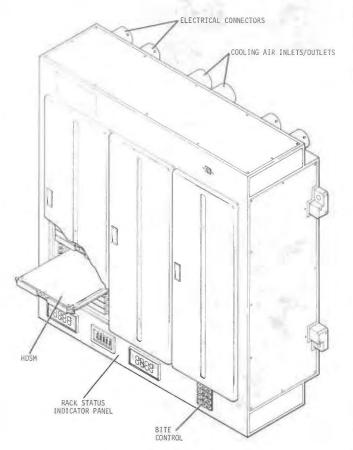

# MIL-STD-1553 DUAL REDUNDANT REMOTE TERMINAL SUPERHYBRID

## BY STEVEN N. FRIEDMAN

# **DOC** ILC DATA DEVICE CORPORATION 105 WILBUR PLACE, BOHEMIA, NEW YORK 11716

ABSTRACT

This paper describes the performance, physical and electrical characteristics of the BUS-65112 Superhybrid, which performs as a fully compliant MIL-STD-1553 Dual Redundant Remote Terminal Unit (RTU).

A discussion of the Custom Monolithic LSI components implemented in the Superhybrid will be included. The RTU's special features and capabilities will be highlighted, along with special programming options which facilitate a broad array of applications.

The BUS-65112 Superhybrid contains all the necessary control lines to allow easy Direct Memory Access (DMA). The interface timing, operational philosophy, and a block diagram highlighting the Superhybrid's functional architecture are included.

### INTRODUCTION

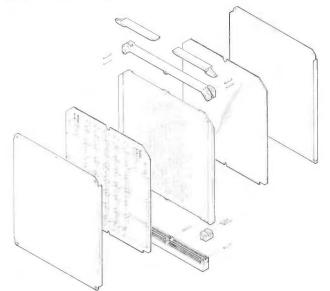

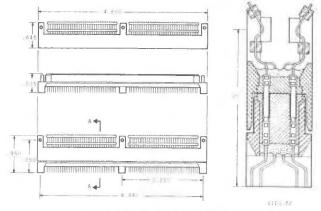

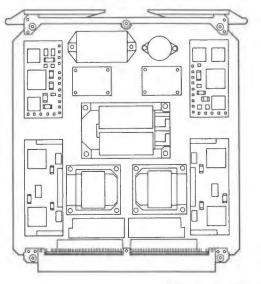

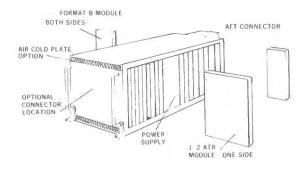

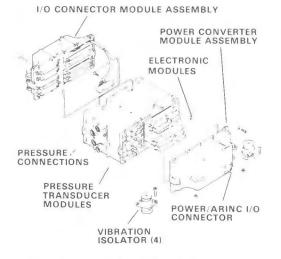

A full array of LSI Monolithic IC's has been developed by ILC Data Device Corporation (DDC) specifically for MIL-STD-1553B RT implementation. It was the development of these LSI Chips that made the BUS-65112 Superhybrid possible. Figure 1 shows the internal placement of the Monolithic devices in the BUS-65112.

Figure 1: BUS-65112 Superhybrid

DDC embarked on an Internal R&D Monolithic Program to attain versatility, small size, low power and reduced end product cost. The development of the four Monolithic IC's really started following the success of the first Monolithic Transceiver. This Monolithic first appeared as the BUS-63105 Transceiver, which replaced the former BUS-8553 discrete version. This Bi-Polar Custom Monolithic not only replaces its predecessor but offers some additional features such as a 12 microsecond encoder input, time-out circuit and a short circuit protected driver output stage, using current limiting. A better mean time between failure (MTBF) computation was realized from the inherently low power density of the Custom Monolithic.

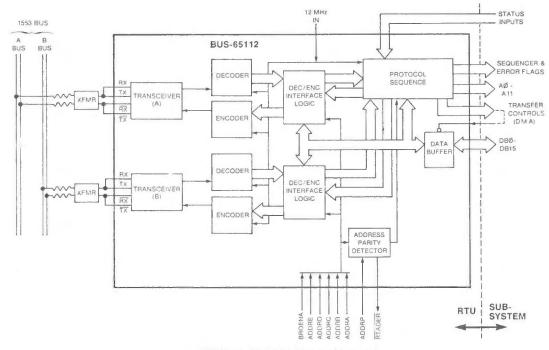

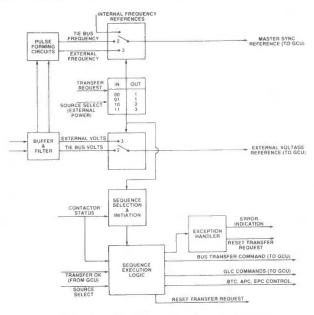

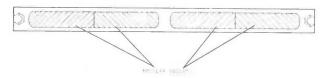

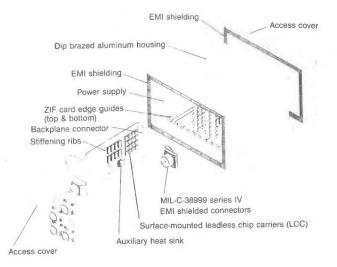

These monolithics were designed to interface with the Harris HD-15530 Encoder/Decoder and include a terminal bit processor (A'), interface logic (AB') and RT protocol sequencer called (B'). Figure 2, BUS-65122 Block Diagram shows how the superhybrid has been configured for implementation of a complete Dual Redundant MIL-STD-1553B Remote Terminal Unit.

The A' terminal bit processor LSI was developed to interface with the Harris Encoder/Decoder, providing Dual Rank Registers and three-state interface buffers that can be used for 8 bit/l6 bit parallel transfers or serial transfers. It was designed to Flag Broadcast and mode code commands if enabled via accessible control lines. It also has 1553 MUX BUS Driver Watch Dog Time-out Logic.

The most important feature of the A' is the Built-In-Test (BIT) capability. This BIT consists of a 16 bit latch that captures the last 16 bit parallel word loaded into the Encoder for transmission. When the word is transmitted onto the 1553 MUX BUS, the transceivers' receiver, if enabled, will then wrap it around to the Decoder, which will permit logic to compare this decoded data with that already stored in the 16 bit latch. If it doesn't match, a Fault Flag is generated.

The AB' LSI Monolithic Multiplex CMOS IC interfaces with the two (A') Terminal Bit Processors and the RTU Protocol (B') Sequence Logic. Its main function is to validate incoming commands from the A' monolithics and then latch key control signals. The two sets of control signals are multiplexed so the 1553 protocol LSI chip sees only one set of key signals. The AB's allow the Dual Redundant 1553 MUX BUS implementation and proper handling of superseding valid commands. It also latches the bit results for the protocol internal bit register.

Copyright © American Institute of Aeronautics and Astronautics, Inc., 1984. All rights reserved.

FIGURE 2. BUS-65112 BLOCK DIAGRAM

The AB' Interface Logic checks each command for a preceeding 2us minimum gap time as required by McAir specifications. It also provides the RT to RT no response time out, handshake fail (HS-FAIL) and status register time outs.

The B', LSI Monolithic MIL-STD-1553B RT Protocol CMOS Logic IC is the key element of the BUS-65112 Superhybrid. It performs all of the Dual Redundant 1553B RTU functions. the B' Protocol supports the following:

COMMAND WORD REGISTER STATUS WORD REGISTER LAST COMMAND WORD REGISTER BIT WORD REGISTER ALL 13 DUAL REDUNDANT 1553B MODE CODES RT to RT, TRANSMITTING RT ADDRESS REGISTER ALL 1553 MESSAGE TRANSFER FORMATS OPTIONAL EXTERNAL PROM FOR ILLEGALIZATION OF MODE CODES AND SUBADDRESS The B' interfaces with the Dual Redundant MUX BUS and handles all 1553 transfer formats. The protocol logic is designed to transfer data in or out of the subsystem interface unit (SSIU) using Direct Memory Access handshake signals (DMA). In conjunction with the DMA type transfers, B' latches the Command Word and generates a Current Word Counter (CWC) which is used to address the proper external RAM locations. All data transfers are 16 bit parallel with a drive capability of 7 TTL loads.

The SSIU has control over the: Terminal Flag, Busy, Subsystem Flag, Message Error, and the Dynamic Bus Acceptance Input Status Register bits. The command word is latched and available throughout a message transfer cycle. There are special output and input signals which will be covered in the discussion of operation.

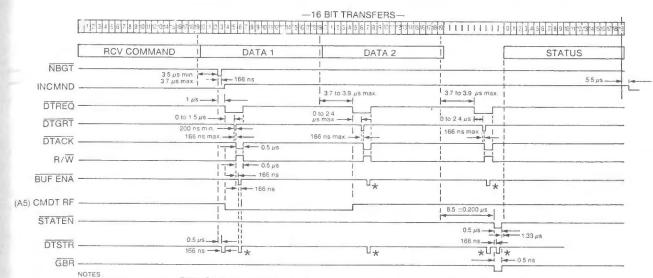

1 - IF A DTGRT IS OMITTED DTACK-MWTR-MCS-DTSTR WILL NOT BE PRESSNT IF DTGRT IS PROVIDED ON THE NEXT DATA TRANSFER A TRANSFER WILL OCCUR → HOWEVER → GBR WILL REMAIN HIGH AND HS FAIL WILL BE ACTIVE 2 - ★ #166 ns PULSE or INTERVAL.

FIGURE 3. BUS-66108 RECEIVE COMMAND TIMING

### DESCRIPTION

The BUS-65112, is a Dual Redundant MIL-STD-1553B Remote Terminal Unit. It contains two transceivers, two Harris HD-15530 Encoder/Decoders, two Terminal Bit Processors, two Interface Logic Blocks, one Protocol Logic Sequencer, CMOS Data Buffers and some miscellaneous logic, such as the address parity detector circuit. It requires two external BUS-25679 MUX BUS Transformers, one 12 megahertz TTL clock input, plus 5 volts, plus or minus 15 volts DC to operate. The BUS-65112 Hybrid measures 2.100" X 1.870" X .250" ht. maximum. This 3.93 square inch package makes use of 78 pins in a Dual-In-Line plug-in package configuration. The Bi-Polar and majority of CMOS devices makes this a very low power Dual Redundant RTU. At idle, the Superhybrid will require approximately 4.2 watts, while at 25 percent duty cycle it will draw 5.2 watts total. All this additional power is not dissipated within the hybrid, but transferred to the 1553 MUX BUS during message transfers.

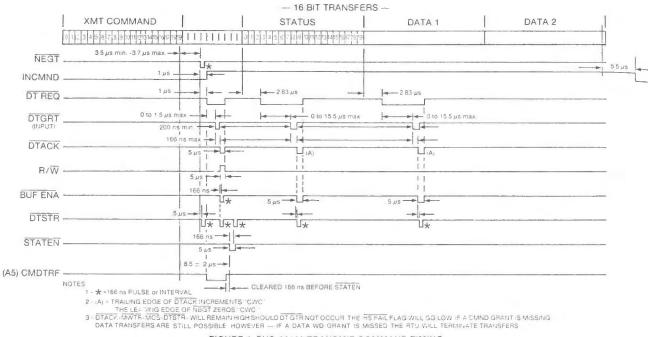

The BUS-65112 has a dedicated internal 16 bit parallel highway which is isolated from the external 16 bit SSIU highway by a set of Bi-Directional CMOS Buffers. The Buffer Enable (PIN 67) signal is brought out to allow the SSIU to monitor the highway at all times or simply when data transfers to the SSIU are being performed. The type of transfer is of a DMA nature in that the RTU requests a transfer, waits for a SSIU Grant and then does the transfer. Figure 3, Receive Command Timing and Figure 4, Transmit Command Timimg, give typical 16 bit transfer details. Note that Data Strobes (DT STR) occur for each DMA transfer cycle and during BUS-65112 internal Command Word and Status Word transfers between the AB' and B' Monolithics. The STATEN signal designates which DT STR is transferring the Status Word Register contents to the A' for transmission.

The B' Protocol converts the external 12MHz clock to 6MHz. The 6MHz is used internally in order to generate and clock all SSIU interface control signals.

FIGURE 4. BUS-66108 TRANSMIT COMMAND TIMING

The Superhybrid generates a 12 bit address field which is used by the SSIU to read or write into memory. Bits A0 - A4 are equal to the Word Count Field (WC) between the NBGT and INCMD period of a normal transmit/receive command. It is always the WC during the process of a Valid Mode Command when INCMD is valid A0 - A4 then becomes the Current Word Counter (CWC) field starting at zero. The trailing edge of DTACK increments the CWC by one. The A5 bit is the Command Transfer Signal (CMDTRF) that tells the SSIU that the DTREQ represents the Valid Command Transfer. The A6 - A10 bits represent the Valid Command Words T/R bit. The AO bit is the least significant bit (LSB), while All is the MSB bit. The Address Field is latched for the entire transfer cycle with the exception of the CWC being incremented for each Data Word Transfer.

### ERROR FLAGS

There are four Error Flags which can be used by the SSIU to detect if anything is wrong with the BUS-65112 terminal. The first is the Message Error (ME) Flag, which

goes low as soon as the RT detects a message error condition, Format Error, Word Count Error, Invalid Words, Sync Error, RT to RT Command Address Error or T/R Bit The second is the RT-FAIL Flag Error. indicating an internal RT failure. The RT FAIL signal indicates when the A' or B' Monolithic devices fail during an RT transmission via the BIT. The Wrap Around Bit Test checks the last word transmitted for incorrect sync type Manchester II The Watch Dog Time-Out also sets Error. this RT FAIL Flag. The RT FAIL Flag is cleared the next time the RT initiates a new status word transmission. The third error flag condition is the Handshake Failure (HS FAIL) which indicates when an SSIU fails to give the required data transfer grant in (DTGRT) in time. If a command word grant is missing, data transfers are still possible, however, if a data word grant is missed, the RT will terminate transfers. The fourth type of output flag is the RT Address Error (RTADERR) which indicates a parity failure on the unique RT address inputs ADDRA thru ADDRP. If one of the hardwired RT address lines should open, the RT ADDERR would flag the problem to the SSIU.

### OUTPUT SIGNALS

The BUS-65112 has a number of useful output signals to interrupt the SSIU such as:

(1) NBGT - New Bus Grant - Low level output pulse used to indicate the start of a new protocol sequence in response to the Command Word just received.

(2) INCMND - High Level Output used to inform the SSIU that the RT is presently servicing a command.

(3) STATEN - Status Word Enable - Low level active output present when the Status Word is enabled onto the 16 Bit Parallel Highway.

(4) BITEN - Built-In-Test Word Enable - Low level used output present when the BIT Register contents is enabled onto the 16 Bit Parallel Highway.

(5) GBR - Good Block Received Word - Low level pulse used to flag the SSIU that a Valid, Legal, Non-Mode Receive Command with the correct number of data words has been received without a message error and successfully transferred to the subsystem.

### SPECIAL OPERATING FEATURES - Inputs

There are two inputs which provide the SSIU with special operating features. The first is the RESET signal. This active low input causes the BUS-65112 to reset all logic, for power-up and initialization sequences. The second special signal is the Broadcast Enable (BROENA), when high allows RT recognition of all ones in the Command Word as a Broadcast Message per MIL-STD-1553B. When low, the RT will not respond to the RT Address 31, unless it was the assigned terminal address.

In addition to the two input signals just described, the BUS-65112 features 6 inputs which provide control of the bits in the Status Word. One of the most unique and useful inputs is the Illegal Command (ILLCMD) which allows the subsystem to illegalize any command or mode code. That means any subaddress or any of the 1553B Dual Redundant Mode Codes not implemented by the SSIU can be illegalized. This can be accomplished by placing a properly programmed PROM across the latched command word outputs. When an illegal pattern presents itself, the PROM will output the illegal flag, which is read by the B' at the proper time. The ME BIT will be set and the RT will transmit the Status Word, but won't transfer any data to or from the SSIU.

The second is the Subsystem Request (SRQ), which is an input from the SSIU used to control the service request bit in the status register. If low when the status word is updated, the bit will be set, if high, it will be cleared. The third is the Accept Dynamic Bus Control (ADBC). An active low input from the SSIU used to set the Dynamic Bus Control Acceptance Bit in the Status Register if the Command Word was a valid, legal mode command for dynamic bus control. The fourth is the Remote Terminal Flag (RT FLAG) used to control the terminal flag bit in the Status Register. If low when the Status Word is updated, the Terminal Flag Bit would be set, if high, it would be cleared.

The fifth signal is the Subsystem Busy (BUSY) used to control the busy bit in the status register. If low when the status word is updated, the busy bit will be set, if high, it will be cleared. If the Busy Bit is set in the status register, no data will be requested from the subsystem in response to a transmit command, on receive commands data will still be transferred to the SSIU. The sixth and last signal is the Subsystem Flag (SS FLAG) used to control the subsystem flag bit in the status register. If low when the status word is updated, the SS FLAG will be set, if high, it will be cleared.

### TYPICAL MODES

The BUS-65112 Superhybrid Protocol Logic, when preparing its response to a command, entertains basically four typical modes. The B' protocol, in determining its proper course of action, looks at the type of command and the associated T/R Bit. The first case is when a Mode Code is received with a T/R = 1, the B' checks the WC4 Bit to see if its zero for no data. This is also performed for reserved Mode Codes. If the WC4 Bit is not zero, the RT transmits the Status Word only. The second case is when a command is received with a T/R = 0, the WC4 Bit = 0, and no data is received, the B' automatically sets the ME bit of the status register and doesn't transmit the status word. The third case is when the WC4 = 1, the T/R Bit = 0, and one and only one data word is received, the RT will respond with a status word only. If no data or too many data words are received, the RT will set the ME Bit and not respond with a status word. The fourth or last consideration is when WC4 = 1 and T/R = 1, but its not a Transmit Bit Word Mode Command or Transmit Last Command Word Mode Command the RT will transmit the Status Word and request one word from the SSIU, unless illegalized by the optional external PROM.

The Bit Word Register is set up using 14 bits to provide the Bus Controller with a full report of the RT's condition. When the RT receives the Transmit Bit Word Mode Command a Status Word followed by the Bit Word is transmitted. The Bit Word is as follows:

SYNC FIELD LSB BIT 15 - NA BIT 14 - NA BIT 13 - CHANNEL B TIME OUT BIT 12 - CHANNEL A TIME OUT BIT 11 - CHANNEL B BIT BIT 10 - CHANNEL A BIT BIT 9 - XMTR B SHUTDOWN BIT 8 - XMTR A SHUTDOWN BIT 7 - BROADCAST RECEIVED BIT 6 - WORD COUNT HIGH BIT 5 - WORD COUNT LOW BIT 4 - ILLEGAL MODE COMMAND BIT 3 - T/R BIT OR MODE CODE ERROR BIT 2 - BIT TEST FAILURE BIT 1 - HANDSHAKE FAILURE MSB BIT 0 - CHANNEL A OR B TIME OUT PARITY

The BIT 12 & 13 Channel A or B Time Out Flags indicate when either of the Watch Dog Timers have exceeded 800 microseconds. The Built-In-Test (BIT), which is continuously being performed with each and every message transfer dynamically, is next. The BIT checks for correct sync, and that there is no Manchester coding or parity errors as well checking the last word wrap-around for each transmission. The transmitter (XMTR) Shutdown for Channel A or B represents when the Mode Command has been exercised. If a Broadcast Command was received, BIT 7 will be set. If a Command with more words or less words than specified in the WC field is encountered, BITS 6 & 5, respectively will be set in the BIT Word Register. If the optional illegal mode command PROM is used, BIT 4 will be set when one is received. The BIT 3, indicates when a Mode Command is received with an incorrect T/R setting. Bit 2, flags when a BIT fault has occurred on either channel. Bit 1, Handshake Fail Flag, is set once a grant is not received on time. The last Bit O indicates when the 1553 Watch Dog Time Out Circuit timed out on either Channel A or B.

### SUMMARY

All of the above features, along with the 14 Bit Built-In-Test Register makes this BUS-65112 a very powerful

remote terminal unit. The Superhybrids small size, low power, low price and flexibility make it an ideal choice in space limited military applications where full 883B level screened parts that can operate from -55 degrees C to +125 degrees C case temperatures are needed. Stephen J. Forde\* and Mark A. Hilmantel\*

Sanders Associates, Inc. Computer Engineering Department Nashua, New Hampshire

### ABSTRACT

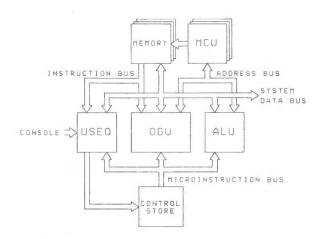

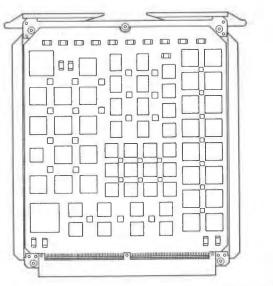

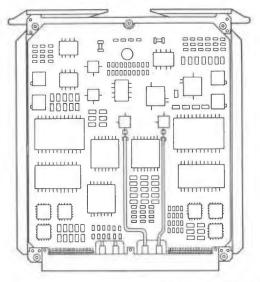

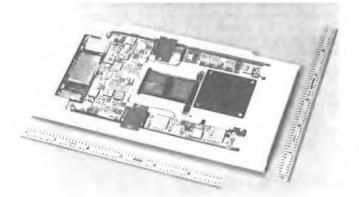

Advanced CMOS processing with line widths of two micrometers makes possible a VLSI implementation of avionics computers. Using a chip set designed with 6000-gate gate arrays has allowed the design of a very high-performance, yet small, low-power, cost-effective, and highly flexible avionics computer.

The chip set comprises four chips: the microsequencer (USEQ), the arithmetic and logic unit (ALU), the operand generator unit (OGU), and the memory controller unit (MCU). The four chips can be configured to implement the Air Force standard instruction set architecture (MIL-STD-1750A, Notice 1) and emulate the Navy standard computers (AN/UYK-20, AN/AYK-14, and AN/UYK-44). An overview of the chip architectures is presented in this paper.

### INTRODUCTION

Today's avionics computers must combine high processing throughput with low power consumption and small size, and yet remain cost-effective and flexible. Meeting such requirements is no easy task, as evidenced by many systems in the field today. Some systems, using emitter-coupled logic, have gained performance at the expense of power; some are too large for airborne requirements; while others have been so optimized for a specific task that they cannot be used for any other purpose. Even those systems which meet the power, size, and flexibility criteria never seem to have the performance needed for many real-time applications.

Many avionic computers have evolved from architectures which were designed to make the best of low-performance core memories [1]. Replacing the core memories with faster semiconductor memories has allowed for some increase in the performance of such machines.

Copyright © American Institute of Aeronautics and Astronautics, Inc., 1984. All rights reserved. However, these machines are limited by the underlying architectures, unable to take full advantage of the performance increases possible with newer technologies. The problem becomes apparent: how to combine technology with suitable architectures to produce a machine which meets the desired performance, power, size, cost, and flexibility objectives. The solution should be obvious: new technologies require new architectures. The remainder of this paper discusses a VLSI chip set which implements this solution.

### THE CHIP SET

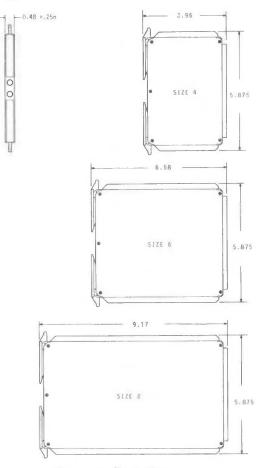

The chip set comprises four chips: the microsequencer (USEQ), the arithmetic and logic unit (ALU), the operand generator unit (OGU), and the memory controller unit (MCU). The four chips can be configured (with appropriate support chips) to implement the Air Force standard instruction set architecture (ISA), MIL-STD-1750A (Notice 1). These same chips can also be used to emulate the Navy standard 16-bit computers: AN/UYK-20, AN/AYK-14, and AN/UYK-44.

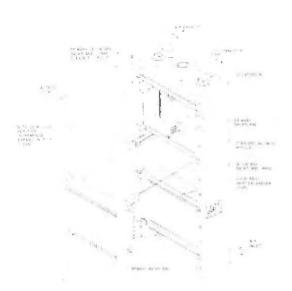

Figure 1 shows a typical configuration for these chips, including memory and support functions. The USEQ, ALU, and OGU chips compose the heart of the central processing subsystem (CPU). The memory subsystem requires at least two independent memory banks, each with its own MCU.

The chip set has been implemented with 2-micrometer CMDS processing. Each chip has the equivalent complexity of a 6000-gate device. The chip set was designed for execution of the DAIS floating-point instruction mix at two million instructions per second (MIPS) and execution of fixed point instructions at 4 MIPS. This performance has been achieved by employing a six-level pipelined CPU, and a memory subsystem with multiple independent banks which allows simultaneous instruction and operand accesses. Power dissipation is 1.1 watts per chip (typical).

<sup>\*</sup> Member IEEE

This work was supported in part by the Naval Research Laboratory under contract N00014-84-C-2250.

### The Microsequencer Chip

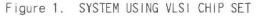

The USEQ chip (Figure 2) decodes instructions from the instruction pipeline and controls microinstruction sequencing. The chip contains five functional units: the instruction queue, the microaddress generator unit (MGU), interrupt processing logic (IPL), the control unit, and the microbranch detect unit (MDU).

The instruction queue buffers machine instructions for decoding and subsequent execution. The queue holds four single-word instructions or two double-word instructions.

The MGU forms the microaddress of the next microinstruction to be executed. The microaddress is derived from the microprogram counter, the microaddress stack, the microliteral (from the current

microinstruction), or from the decoded machine instruction. The microaddress is used to access the off-chip control store.

The IPL maintains surveillance of various internal and external fault flags, forcing interrupt processing to occur as necessary. The IPL receives data (e.g. interrupt masks) via the system data bus. Also included in this unit are timers which can be used as watchdog timers or real-time clocks. These timers are also loaded via the system data bus.

The control unit receives microinstructions from the control store and uses these primarily for controlling the formation of the next microaddress. This unit also receives the microliteral field of the microinstruction, which is used in forming the next microaddress. The MDU maintains surveillance of internal status flags and detects conditions which require microbranching. Control signals are provided from the ALU chip for branching. These controls insure that the instruction queue contains the proper sequence of machine instructions.

Figure 2. MICROSEQUENCER BLOCK DIAGRAM

### The Arithmetic and Logic Unit Chip

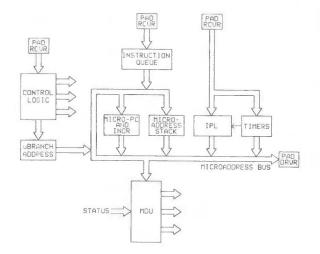

The ALU chip (Figure 3) uses a 32-bit internal architecture to perform both fixed-point and floating-point operations. The chip has four functional units: the ALU, the program status unit, the control unit, and an external interface.

The ALU portion of the chip comprises a set of pipeline registers and an accumulator. They are configured as pairs of 16-bit registers, each 16-bit register is provided with individual controls so that both singleand double-precision operands can be handled efficiently. The ALU, shifter, and floating-point unit (FPU) are each 32-bits wide. These units are connected to an internal 32-bit bus. Results of operations are placed on this bus, where they may either be sent out on the system bus or used as operands during subsequent operations. The chip interfaces with other system elements via three 16-bit buses. All three are tri-state; two are bidirectional. Two buses supply data operands to the ALU. The results of ALU operations are sent over the system data bus (16 bits at a time, controlled by the external interface), or additionally, over the bidirectional data operand bus. This capability is particularly useful for double-precision operations which require one of the words of the result to be reused (e.g. double-precision multiply).

The program status unit maintains the machine state, using status flags (e.g. carry, overflow,etc.) from the ALU, shifter, and FPU, as well as data on the internal data bus.

The chip receives encoded instructions from the control store. These instructions are decoded by the control unit and routed to the appropriate circuits on the chip.

Figure 3. ALU BLOCK DIAGRAM

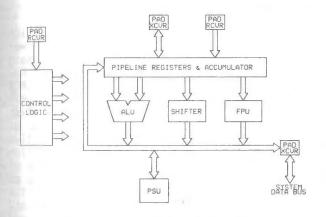

### The Operand Generator Unit Chip

The OGU chip (Figure 4) is tasked with providing the data operands to the ALU chip. These operands come from the register file or from memory. In the latter case, the OGU provides the data memory address to the memory controller chip.

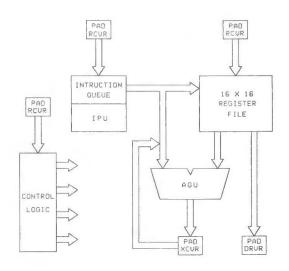

The chip is divided into five functional units: the instruction queue, the instruction prefetch unit (IPU), the register file, the address generator unit (AGU), and the control unit.

The instruction queue is an exact copy of the instruction queue on the microsequencer chip. The instructions are buffered on the OGU to provide the register addresses for machine instructions. The controls for the instruction pipeline (on both the OGU and the USEQ chips) originate from the IPU. The IPU uses information in each microinstruction, as well as signals from the microbranch detect unit and program status unit on the USEQ and ALU chips, to keep the pipeline filled.

The register file on the OGU consists of sixteen 16-bit registers, addressed by a read address and a write address. It allows two read operations and one write operation per machine cycle. Data read from the register file can be used as data by the ALU and/or used to compute a logical memory address by the address generator.

The address generator unit's primary function is to calculate logical addresses. This unit allows memory-indexed operations to execute in a single machine cycle, saving time and control store space. The AGU is also used to adjust operands before being piped to the ALU.

The control unit on the OGU, in addition to decoding microinstructions, controls pipeline data bypass logic. Bypass operations allow the CPU to proceed, without waiting, when one instruction execution requires the result value of the immediately preceding instruction. Without the bypass logic execution would be delayed while the needed operand flows through the pipeline.

Figure 4. OGU BLOCK DIAGRAM

### The Memory Controller Unit Chip

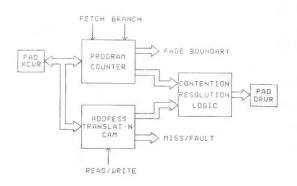

The MCU gate array (Figure 5) controls a single bank of up to 128K words of memory. It provides the following capabilities: dual-port control with contention resolution; multi-mode logical-to-physical address translation; read/write/execute protection; and a program counter for instruction port accesses.

The Memory Controller transfers information to and from the rest of the computer via the address bus. This information includes logical addresses, physical addresses, protection flags, and fault codes.

Memory data does not pass through the Memory Controller gate array, but instead is gated to/from the instruction or data bus by signals generated in the memory controller; this reduces the number of pins required on the gate array.

The Memory Controller is able to accept two simultaneous memory requests, one for instructions and one for operand data. Instruction addresses come from the on-chip program counter (except in the case of program branches) in order to reduce the number of wires connecting the memory with the CPU. Operand addresses come from the OGU chip via the address bus. In most cases, the two requests are handled simultaneously by memory controllers in separate banks. Occasionally, both requests must be serviced in the same bank; the memory controller contention resolution logic then sequences the operations on the memory array.

A content-addressable memory (CAM) allows logical-to-physical address translation and protection operations to occur simultaneously with address decoding, increasing throughput when translation is required. When an address is not found in any memory controller's CAM, the CAM is updated by the CPU.

### Figure 5. MEMORY CONTROLLER CHIP BLOCK DIAGRAM

# SUMMARY

Today's avionic computers must combine high processing throughput with low power consumption and small size, and yet remain cost-effective and flexible. New architectures implemented with advanced CMOS gate arrays have resulted in a highly flexible VLSI chip set, capable of executing the DAIS floating-point instruction mix at VHSIC speeds. The floating-point execution rate of 2 MIPS and fixed-point instruction rate of 4 MIPS, surpasses the performance of other machines of equal size and power by as much as 50-100%. These chips implement the MIL-STD-1750A (Notice 1) 16-bit ISA and emulate the AN/AYK-14, AN/UYK-20, and AN/UYK-44 standard computers.

## REFERENCES

[1] R. J. Garbos, "High Performance Avionic Architectures", GOVERNMENT MICROCIRCUIT APPLICATIONS CONFERENCE (GOMAC) 1984 DIGEST OF PAPERS VOL. 9, November 1984.

# SESSION 22 AIRBORNE

# AIRBORNE SEPARATION ASSURANCE

Chairman:

Frank Chandler Sperry Dalmo Victor, Inc.

Joseph J. Fee Federal Aviation Administration

This session provides an understanding of the plans, designs, experiences and problems concerning current and future collision avoidance systems and select mode transponders.

22

### EVOLUTION OF THE COLLISION AVOIDANCE SYSTEM IN THE COCKPIT

### William L. Hyland

### Federal Aviation Administration Washington, D.C.

### Abstract

Collision Avoidance Systems have been in various stages of development for a number of years. The aviation community is now on the verge of adopting the Traffic Alert and Collision Avoidance System (TCAS) for operational implementation. The majority of efforts over these development years have been devoted to the engineering aspects of the systems. As the system's concepts matured, the emphasis on the pilot use of the system has increased, with the attendant impact on system design of these evolutions. This paper treats the cockpit side of the systems evaluation, and the evolution of operational concepts over these years.

### Introduction

The development of methodologies and systems for reducing the potential of aircraft midair collisions has been underway since the <u>second</u> airplane took off. Much effort has been expended by engineers and pilots to improve the capabilities of pilots to visually acquire and avoid potentially threatening aircraft. Many years of experience have produced the present "rules of the road", and pilot procedures for "seeing-and-avoiding" other aircraft. Special aircraft paint and visual alerting devices, such as navigation lights, beacons and strobe lights have improved those capabilities. The air traffic control radar has improved the system for IFR and controlled aircraft.

In recent years, more active collision avoidance systems have been proposed and evaluated to further improve these capabilities. In 1966, the airline community proposed an airborne system for air carrier use based on dedicated equipments for all users, operating at 1600 -1615 MHz. (1). This system became known as the Airborne Collision Avoidance System (ACAS). The FAA began development testing of a ground based collision avoidance system in 1974, designed to operate in the existing air traffic control radar beacon band at 1030-1090 MHz. This system, known as Intermittant Positive Control (IPC) (2) was intended for the general aviation community.

In 1975, the FAA began development of an <u>airborne</u> beacon-based system, known as BCAS. As the benefits of the beacon-based solution became more evident, the FAA in 1976 (3) proposed a combination of airborne and ground systems to improve "Airborne Separation Assurance" (ASA). In 1981, the FAA eliminated the ground-based portion of ASA and the Traffic Alert and Collision Avoidance System (TCAS) became the final system of choice.

Through the above progression of systems, evaluation of use of the devices in the cockpit has progressed from none to comprehensive. As pilots began to be more involved in the systems,

This paper is declared a work of the U.S. Government and therefore is in the public domain.

573

changes in performance of the systems were introduced. Although little change in the basic concepts of the radio frequency (r.f.) portions of the system occured, the requirements for warning times needed by the pilot and the impact of rates at which alerts were experienced had considerable influence on the overall system design.

### **Barlier Systems**

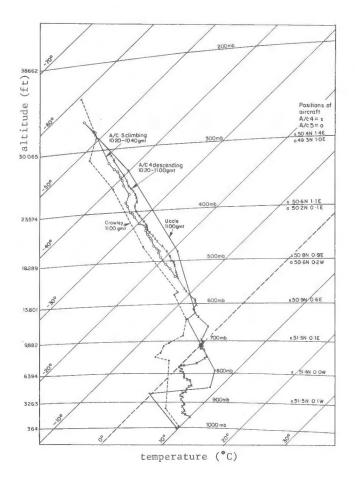

The ACAS envisioned by the airlines was basically an alerting system developed to deliver collision avoidance "commands" to the pilot. For display of this information, the system integrated the collision avoidance commands with an existing Instantaneous Vertical Speed Indicator (IVSI) instrument. The threat algorithm developed provided alerts with a 40-second and 25-second "time-to-collision" (TAU) and altitude separation of up to 3400 feet. The threat criteria produced the following commands:

| Limit | descend | to | 2000'  | Limit | climb | to | 2000'        |

|-------|---------|----|--------|-------|-------|----|--------------|

| Limit | descend | to | 1000'  | Limit | climb | to | 1000'        |

| Limit | descend | to | 500'   | Limit | climb | to | 500 <b>'</b> |

| Don't | descend |    |        | Don't | climb |    |              |

| Climb |         |    | Descei | nd    |       |    |              |

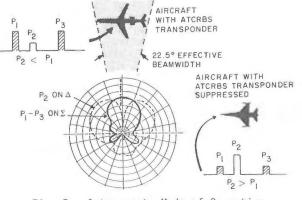

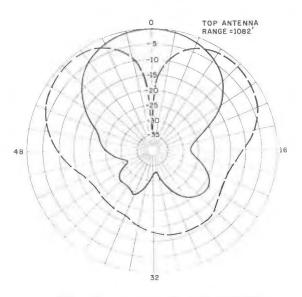

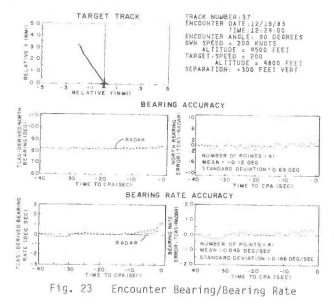

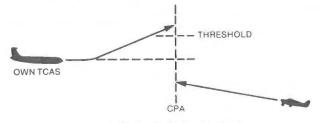

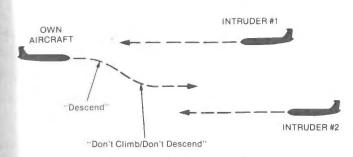

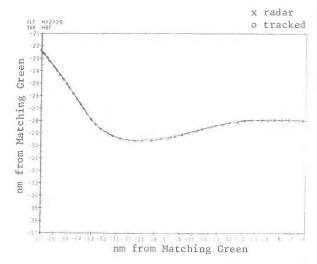

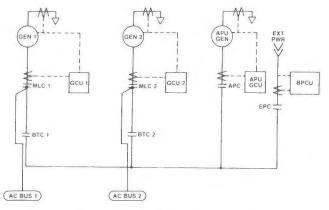

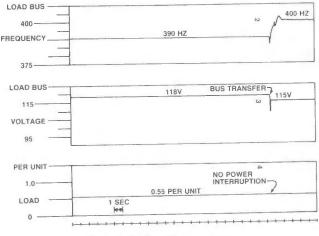

The integrated display (figure 1) provided a red climb or descend arrow, with segmented amber lights around the ring for limit rates. Because of the perceived need to control the environment when "commanding" a pilot to maneuver vertically, the display further instructed the pilot to "Don't Turn"! Pilot organizations found these proposed methodologies acceptable. However, there remained some concerns for the impact on the ATC system, and for possible false alarms.

### Figure 1

While no actual pilot evaluations in operational environments were conducted, an ATC simulation was conducted to assess the CAS impact on the operating environment (4). It was found that the rate of cockpit alerts in the dense terminals would be excessively high because of the large protection volume, and that the phase of flight and location in the pattern at which the high number of alerts would occur would unnecessarily disrupt the ATC system. Commands were being generated with the "don't turn" instruction, which when delivered in the approach phase confused the overall air traffic control situation.

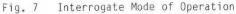

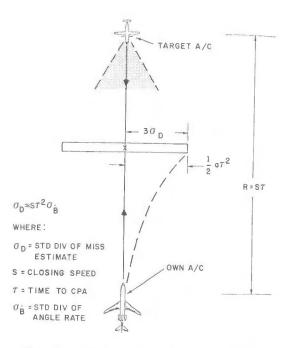

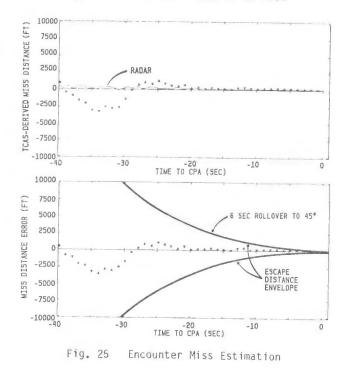

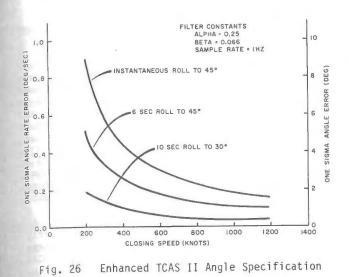

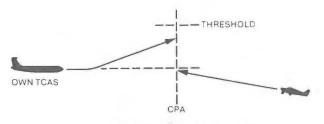

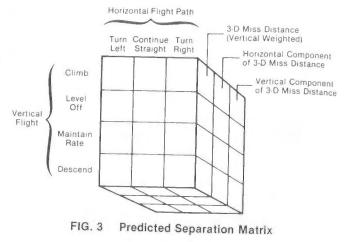

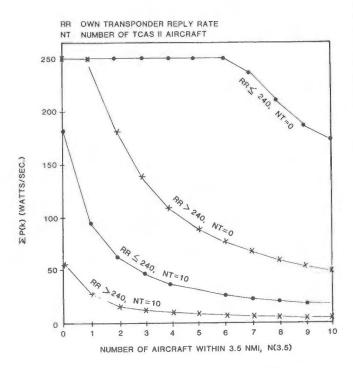

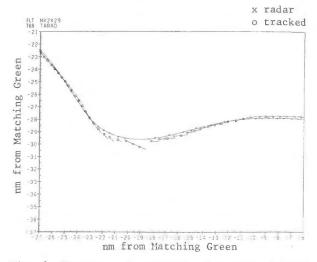

The ground-based system, IPC (later known as Automatic Traffic Advisory and Resolution System, ATARS), originated from a background of general aviation proximity warning systems, and had developed into a more complex system with maneuver commands. It was intended for delivering horizontal as well as vertical maneuver commands. The display developed for panel mounting (figure 2) provided the following:

Climb/Don't Climb Turn Right/Don't Turn Right Descend/Don't Descend Turn Left/Don't Turn Left

It did not use the IVSI or "limit rate" commands. The display also provided course bearing information on intruder traffic, in clock position lights, and altitude information at these clock positions displayed as "above", "coaltitude" or "below".

Figure 2

Some actual experience was gained in flying the IPC (5), although at this point the concept emphasized the general aviation environment and relied on VFR conditions and visual acquisition in most cases. A concept of priorities of alerts was conceived to first alert a pilot to a threat, and finally to maneuver. It used a decreasing time to collision (TAU) threat volume to generate these alerts. Many of the conclusions reached in these tests were as a result of the visual acquisition of the target aircraft. At this point the traffic advisory feature in VFR environments gained support.

### BCAS and IPC

When the decision was made by the FAA to support a beacon-based collision avoidance system mainly because of the large number of operating transponder equiped aircraft, the operational concepts of ACAS and IPC were integrated. A lower cost active BCAS (i.e., actively interrogating other aircraft) would operate when out of ground radar coverage, providing vertical-only commands. A passive BCAS (i.e., listening to replies in response to ground interrogation) would operate within radar coverage and provide horizontal commands as well as range, bearing and altitude information. The IPC, which relied on use of the ground-based beacon system to derive collision avoidance data and transmit information, would individually tailor the threat volumes in terminal environments to reduce alert rates in the denser terminal areas. At this point a cockpit simulation of the BCAS and IPC operation was conducted with airline pilots to select suitable display(s) for further CAS testing (6). This

cockpit evaluation determined acceptable displays, using integrated instruments (e.g., IVSI), CRTs and LED techniques. In integrating the displays, the general aviation IPC display was dropped and CRT techniques used. This allowed display of range from IPC not formerly possible with the general aviation IPC display. Pilots felt that altitude, range, relative bearing and heading of the threat aircraft was essential, in that order. Seventy-nine percent felt the traffic information was essential. The integrated IVSI display was again found acceptable because of the obvious combining of vertical rate information with vertical CAS maneuver commands, and a plan view display for traffic information was preferred, when the information was available.

In this time period, the BCAS alert rate subject was readdressed in ATC simulations. The "vertical only" active BCAS was still functionally quite similar to ACAS. The requirement to prevent turning when "commanding" a manuever was dropped to minimize unnecessary ATC impact. Also the idea that a pilot had no choice in the matter was modified and the idea that a "resolution advisory" would be provided to the pilot was adopted, assuming a pilot always retained his own decision authority. In the ATC simulations (7), the continuing high alert rate, largely because of the 40-second TAU alert, was reconsidered. The algorithm was reconfigured to provide a softer advisory; i.e., a "limit rate" advisory when appropriate, but within the same time reference as the resolution advisory; i.e., 25 seconds and not using the wider absolute altitude band. This reduced the alarm rates, but still provided the pilot only a limited number of change-of-direction instructions. Features were included to desensitize or reduce the threat volume for each aircraft similar to the technique used for the IPC; i.e., 30 seconds, 25 seconds and 20 seconds TAU, but based on altitude. It was recognized that the protection volume would be reduced as the aircraft entered the terminal areas (with decreasing altitude), but this was a trade-off with alert rates, the continuing concern of the user. This reduced threat volume was also consistant with reduced spacing criteria applied by ATC in the terminal areas. Traffic advisory information would remain an option.

Equipments were procured and a system installed on an operating Piedmont Airlines air carrier, with an integrated IVSI display located in the observer's position to gather more data in the operating environment. For the benefit of the observers and to gather information on the traffic advisory feature while in an air carrier cockpit, coarse bearing, range and encoded altitude information was provided on a CRT. These tests noted a high number of unnecessary alerts from onthe-ground aircraft, a relatively "acceptable" rate on the remaining alerts, and some, although not universal, interest in the traffic advisory feature (8). Concerns for "false" alerts; i.e., maneuver instructions on non-existent aircraft did not appear to be a factor. It began to be noted, however, that most of the resolution advisories that did occur were instructing maneuvers that were the same as a maneuver about to be made, was already in progress, or visual acquisition was made and could be ignored. The unnecessary alerts on the ground could be eliminated by technical

solutions, but what was the altitude of the pilot toward the alerts that he didn't need to follow? Most did not find them objectionable as long as the rate was low, and the rate was low. This experience in live air carrier environments began a much closer observation of the pilot reactions to the BCAS information.

In June 1981, a decision was made to pursue only the airborne solution to CAS, the TCAS. The ATARS was deleted, and all efforts focused on the active system. With this commitment, a sequence of air carrier cockpit simulations and limited flight tests was conceived to more closely assess pilot reactions to the maneuver and traffic advisory information.

When preparations for these tests were made, two opposing positions emerged on the traffic advisory feature, which had become one of the principal issues of cockpit implementation of TCAS. Against the traffic advisory was the obvious competition for scarce panel space for another display, possible distraction of the pilot in denser areas with information perhaps not necessary when on IFR flight plans, and possible overuse and contention with ATC for approach management. It was felt to be an expensive "option". This faction generally also felt that the IFR oriented air carrier pilots would follow the resolution advisories automatically when in IFR conditions, and that following the resolution advisories must be mandatory at all times making a traffic advisory display superfluous.

The other faction felt that pilots needed to have advance information on threatening traffic before maneuvering, that traffic advisories were essential to permit pilots to correlate resolution advisories with aircraft in sight, and that pilots could make their own decision on whether to follow the resolution advisories if better information was available.

In response to the above concerns, a methodology was adopted to 1) share the panel space by using the already developed Integrated IVSI for resolution advisories and the Weather Radar display for traffic advisory information (figure 3), 2) test for pilot response in cockpit simulations of IMC conditions, and in operational airspace under VMC conditions, and 3) select display methodologies to limit the distraction to the pilots but still provide him the intended information.

The first cockpit simulation (9) established audio and visual alerting criteria, and added voice reinforcement to the advisories. Color variations in CRT display methodologies for traffic advisories were included (although color was not necessarily required) to depict the priority of alerts; i.e., white for information, amber for caution, and red for warning. These and the integrated IVSI were accepted for further evaluation.

In conducting the operational flights in a twin engined C-421 at Lincoln Laboratory (10), a concept for the use of traffic advisory information was defined. To determine the pilots ability to use the information for only TCAS related potential threats, and not to manage flight paths, the weather radar display was

### Figure 3

activated with the traffic situation only when TCAS identified a potential threat. Also, a pilot option to check the information on a request basis for a 15 second time-out period was provided. An additional factor developed during the tests was the need to consider traffic advisiories on all beacon traffic, including aircraft without Mode C and this feature was added for evaluation. Several optional ranges, and different numbers of displayed targets within those ranges were evaluated. It was decided to display all aircraft within 4 miles and + 1200 feet of own aircraft wherever any potential threat aircraft activated the traffic display to enable the pilot to be aware of this "situation" at the time of alert. Also, because of pilot concern for the inability to ascertain the vertical direction of the threat, a vertical direction arrow was added to the threat traffic information if its rate exceeded 500 fpm. The workload of the traffic advisory did not seem excessive.