# United States Patent [19]

#### Garner

# [11] Patent Number:

5,724,592

[45] Date of Patent:

Mar. 3, 1998

| CESSOR |

|--------|

| E      |

|        |

[75] Inventor: Richard P. Garner, Cameron Park,

Calif.

[73] Assignee: Intel Corporation, Santa Clara, Calif.

[21] Appl. No.: **760,325**

[22] Filed: Dec. 5, 1996

## Related U.S. Application Data

| [63] | Continuation | of | Ser. | No. | 414,190, | Mar. | 31, | 1995, | aban- |

|------|--------------|----|------|-----|----------|------|-----|-------|-------|

|      | doned.       |    |      |     |          |      |     |       |       |

| [51] | Int. | Cl.6 |  | G06F | 1/32 |

|------|------|------|--|------|------|

|------|------|------|--|------|------|

[52] U.S. Cl. ...... 395/750.04; 395/430; 395/494

## [56] References Cited

#### U.S. PATENT DOCUMENTS

| 4,545,030 | 10/1985 | Kitchin .      |         |

|-----------|---------|----------------|---------|

| 4,644,494 | 2/1987  | Muller .       |         |

| 4,758,945 | 7/1988  | Remedi .       |         |

| 4,851,987 | 7/1989  | Day.           |         |

| 4,853,560 | 8/1989  | Iwamura et al  |         |

| 5,008,566 | 4/1991  | Hashimoto .    |         |

| 5,070,474 | 12/1991 | Tuma et al     |         |

| 5,086,387 | 2/1992  | Arroyo et al   | 395/551 |

| 5,148,380 | 9/1992  | Lin et al      |         |

| 5,167,024 | 11/1992 | Smith et al    | 395/750 |

| 5,184,031 | 2/1993  | Hayakawa et al |         |

| 5,189,647 | 2/1993  | Suzuki et al              |

|-----------|---------|---------------------------|

| 5,193,198 | 3/1993  | Yokuchi .                 |

| 5,291,542 | 3/1994  | Kivari et al              |

| 5,369,771 | 11/1994 | Gettel .                  |

| 5,426,755 | 6/1995  | Yokouchi et al 395/425    |

| 5,428,579 | 6/1995  | Robinson et al 365/230.03 |

| 5,524,230 | 6/1996  | Sakaue et al 395/430      |

| 5,590,341 | 12/1996 | Matter 395/750            |

| 5,602,987 | 2/1997  | Harari et al 395/182.06   |

|           |         |                           |

#### FOREIGN PATENT DOCUMENTS

| 2088442   | 7/1993  | Canada .          |

|-----------|---------|-------------------|

| 0392895A2 | 10/1990 | European Pat. Off |

| 2251323   | 7/1992  | United Kingdom.   |

| 2251324   | 7/1992  | United Kingdom .  |

#### OTHER PUBLICATIONS

Robinson, Kurt, "Trends in Flash Memory System Design", Wescon Conference Record, Nov. 1990, pp. 468-472.

Primary Examiner—Jack B. Harvey

Assistant Examiner—Jeffrey K. Seto

Attorney, Agent, or Firm—Blakely, Sokoloff, Taylor &

Zafman

## [57] ABSTRACT

A flash electrically-erasable programmable read only memory (EEPROM) array and a method for allowing a host computer to detect a plurality of different power-expending modes into which a storage device may be placed for operation, to select a particular one of those modes to match the power abilities of the host computer, and then to place the storage device in the proper power mode of operation to best function with the host system.

#### 23 Claims, 3 Drawing Sheets

U.S. Patent

Figure 3

#### METHOD AND APPARATUS FOR MANAGING ACTIVE POWER CONSUMPTION IN A MICROPROCESSOR CONTROLLED STORAGE DEVICE

This is a continuation of application Ser. No. 08/414,190, filed Mar. 31, 1995, now abandoned.

#### BACKGROUND OF THE INVENTION

#### 1. Field Of The Invention

This invention relates to microprocessor controlled storage devices such as flash EEPROM memory arrays, and more particularly, to methods and apparatus for managing power consumption in such storage devices.

#### 2. History Of The Prior Art

Recently, microprocessor controlled storage devices such as flash EEPROM memory arrays have been used as a new form of long term storage. A flash EEPROM memory array is constructed of a large plurality of floating-gate metaloxide-silicon field effect transistor devices arranged as memory cells in typical row and column fashion with circuitry for accessing individual cells and placing the memory transistors of those cells in different memory conditions. Such memory transistors may be programmed by storing a charge on the floating gate. This charge remains 25 the several views. when power is removed from the array. The charge level may be detected by interrogating the devices. These arrays may be designed to provide a smaller lighter functional equivalent of a hard disk drive which operates more rapidly and is not as sensitive to physical damage. Flash EEPROM memory arrays are especially useful in portable computers where space is at a premium and weight is extremely

In order to allow flash EEPROM memory arrays to accomplish the storage functions normally accomplished by 35 electro-mechanical hard disk drives, one type of flash memory manufactured by Intel Corporation of Santa Clara, Calif., includes a microprocessor which controls many of the functions of the storage device such as loading commands and data which are used by the storage device for accomplishing various housekeeping, setup, and other functions. The same storage device also includes hardware apart from the microprocessor which is especially designed to respond to the commands and utilize the data to accomplish the storage of data in the memory array. Power must be supplied for operating all of these components.

Although these memory arrays were initially designed for use in portable computers, their desirable characteristics has devices such a desktop computers and personal digital assistants (PDAs). To a great extent, this expansion has occurred along with the expansion of the PCMCIA bus into these other forms of digital devices. One problem created by in these different uses vary widely. Thus, with PDAs and very small portable computers, a few double A batteries may supply the power; while desktop computers may provide very large amounts of power.

It is desirable to allow any storage device designed for 60 portable, PCMCIA, or removable use to function with as many different types of digital systems as possible. However, in order to accomplish this, it is necessary that the storage device be capable of utilizing as little power as possible when functioning with low powered systems. To 65 accomplish this, it is desirable to allow such storage devices to function at the lowest level of power possible.

#### SUMMARY OF THE INVENTION

It is, therefore, an object of the present invention to provide apparatus and a method for managing the power used by microprocessor controlled storage devices so that the storage device may be used in a plurality of different digital systems.

It is another object of the present invention to reduce automatically the power used by components of flash EEPROM memory arrays to a level compatible with a particular host system.

These and other objects of the present invention are realized in a flash EEPROM memory array by circuitry and a method for allowing a host computer to detect a plurality of different power-expending modes into which a storage device may be placed for operation, to select a particular one of those modes to match the power abilities of the host computer, and then to place the storage device in the proper power mode of operation to best function with the host system.

These and other objects and features of the invention will be better understood by reference to the detailed description which follows taken together with the drawings in which like elements are referred to by like designations throughout

#### BRIEF DESCRIPTION OF THE DRAWINGS

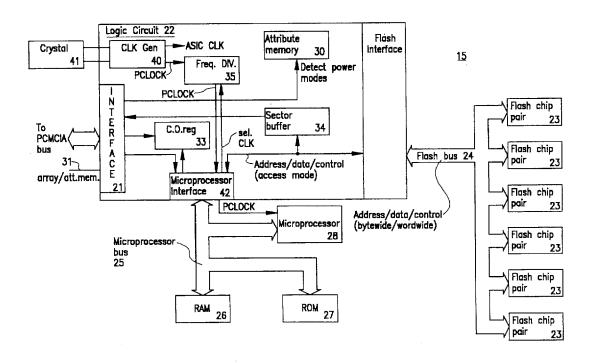

FIG. 1 is a block diagram of a computer system which may utilize the present invention.

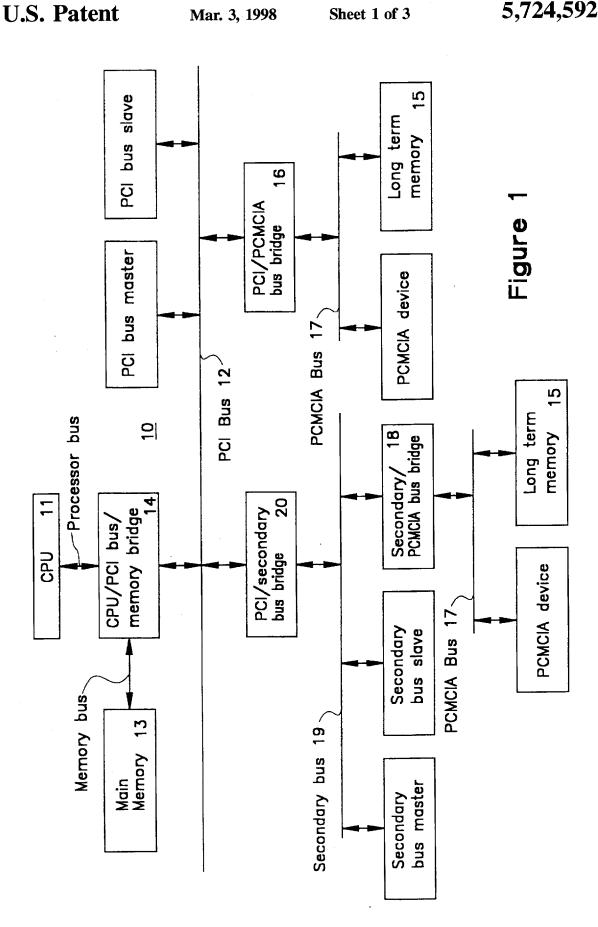

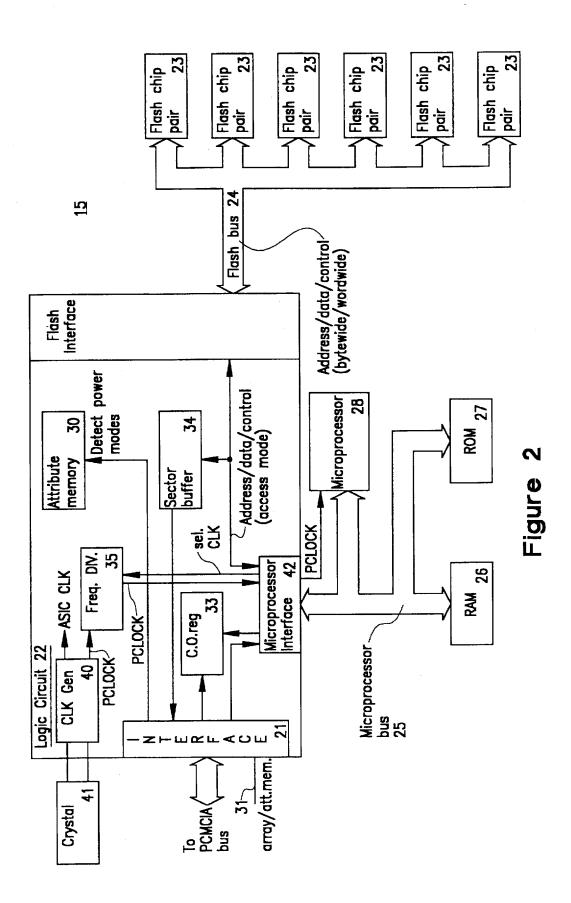

FIG. 2 is a block diagram of a flash EEPROM memory array constructed in accordance with the present invention.

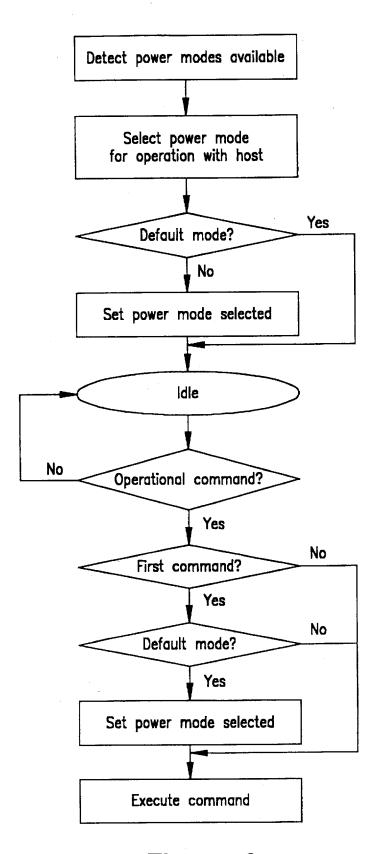

FIG. 3 is a flow chart describing the operation of a portion of the memory array in carrying out the present invention.

### NOTATION AND NOMENCLATURE

Some portions of the detailed descriptions which follow are presented in terms of symbolic representations of operations on data bits within a computer memory. These descriptions and representations are the means used by those skilled in the data processing arts to most effectively convey the substance of their work to others skilled in the art. The operations are those requiring physical manipulations of physical quantities. Usually, though not necessarily, these quantities take the form of electrical or magnetic signals various read, write, and erase functions necessary to the 45 capable of being stored, transferred, combined, compared, and otherwise manipulated. It has proven convenient at times, principally for reasons of common usage, to refer to these signals as bits, values, elements, symbols, characters, terms, numbers, or the like. It should be borne in mind, allowed their use to expand into other forms of digital 50 however, that all of these and similar terms are to be associated with the appropriate physical quantities and are merely convenient labels applied to these quantities.

Further, the manipulations performed are often referred to in terms, such as adding or comparing, which are commonly this expansion has been that the sources of power available 55 associated with mental operations performed by a human operator. No such capability of a human operator is necessary or desirable in most cases in any of the operations described herein which form part of the present invention; the operations are machine operations. Useful machines for performing the operations of the present invention include general purpose digital computers or other similar devices. In all cases the distinction between the method operations in operating a computer and the method of computation itself should be borne in mind. The present invention relates to a method and apparatus for operating a computer in processing electrical or other (e.g. mechanical, chemical) physical signals to generate other desired physical signals.

# DOCKET A L A R M

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

# **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

## API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.