| · _ :.: | . : 17 |     | (a     |         |

|---------|--------|-----|--------|---------|

| PCMC    | JIA PC | CAR | ID STA | NDARD   |

|         |        |     |        | ace 2 1 |

.2-3

## Contents

### LIST OF TABLES

CLEVELAND PUBLIC LIBRARY SCIENCE & TECHNOLOGY DEPT.

## JUL 28 1994

STANUARDS

## 1. GENERAL

List of Tables .....

1.1 Introduction

1-3

1.2 Relationship to Other Standard-Setting Bodies

1-3

1.3 History

1-3

1.4 Standardization Goals

1-3

1.5 Differences Between Release 1.0 and 2.0

1-4

## 2. SCOPE

| 2.1 Elements of the Stand | lard: Physical, Interface, Software |  |

|---------------------------|-------------------------------------|--|

|                           |                                     |  |

|                           |                                     |  |

|                           |                                     |  |

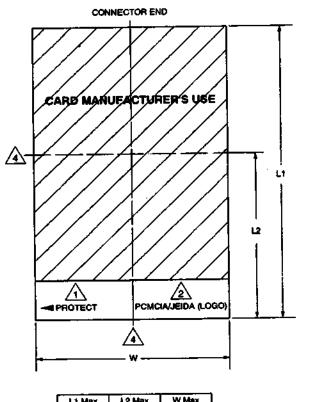

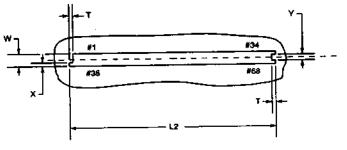

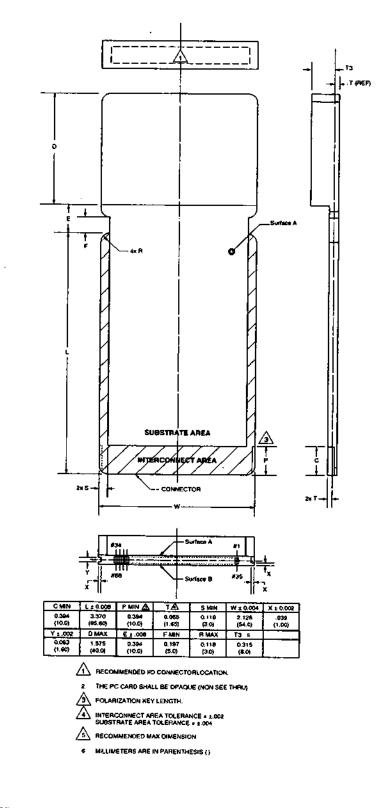

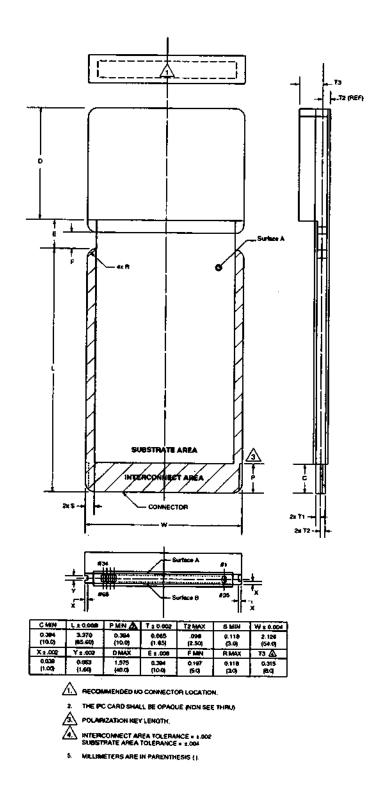

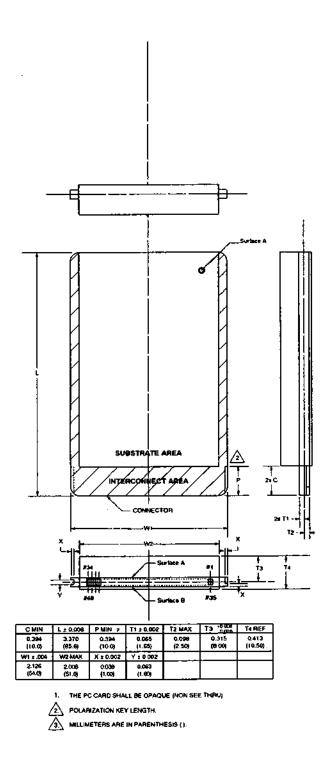

## 3. CARD PHYSICAL

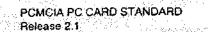

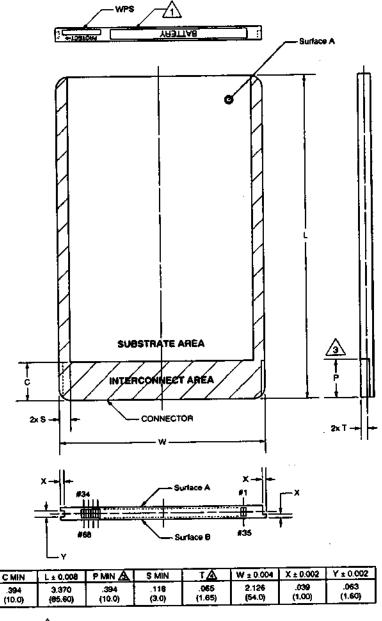

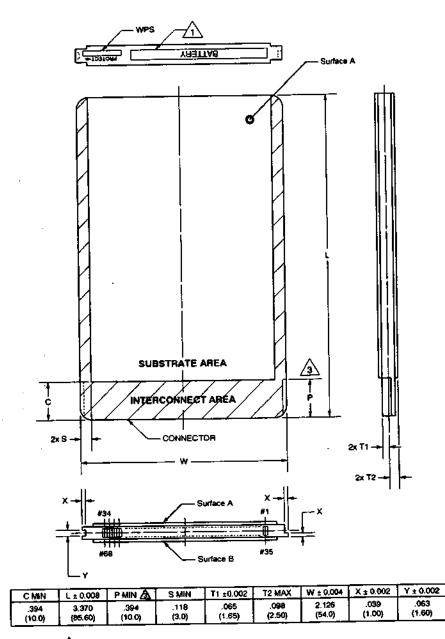

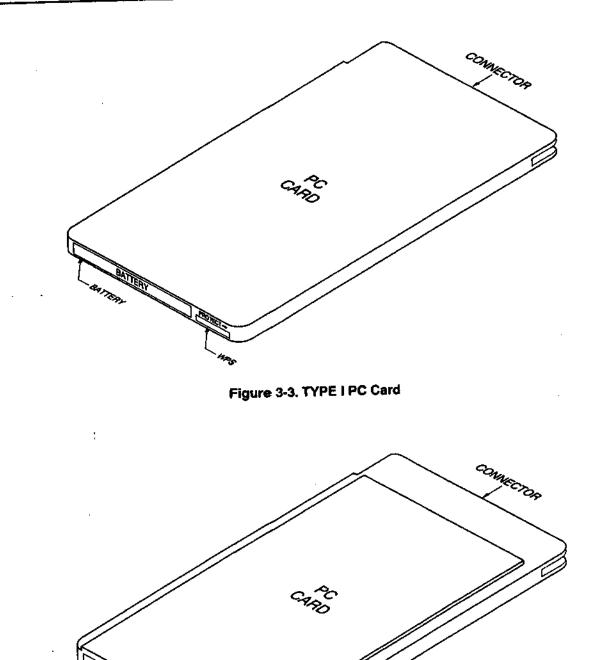

| 3.1 Card Dimensions                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 Write Protect Switch (WPS)      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.1.2 Battery Location              | <br>1999 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 19 |

|                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

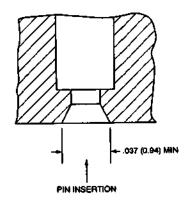

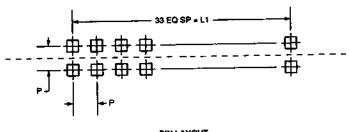

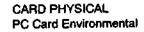

| 3.2 Connector                       | <br>en gan en latte<br>Traductionen (Traduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

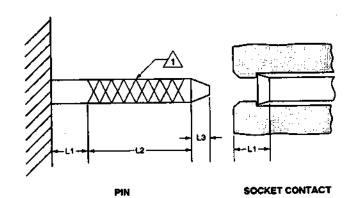

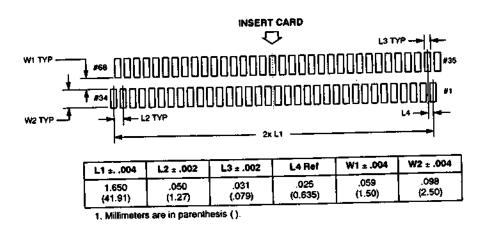

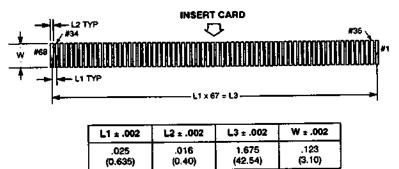

| 3.2.1 Card Connector                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

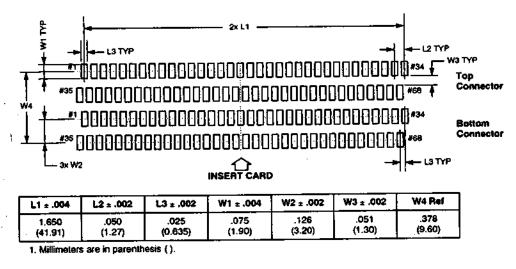

| 3.2.2 Host Connector                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

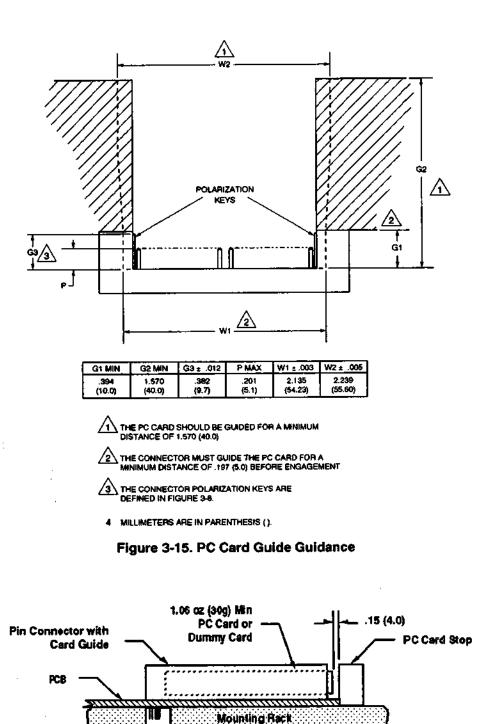

| 3.3 PC Card Guidance                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4 Connector Reliability           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1 Mechanical Performance        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.1 Office Environment          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.2 Harsh Environment           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.3 Total Insertion Force       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.4 Total Pulling Force         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.5 Single Pin Pulling Force    | · .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.4.1.6 Single Pin Holding Force    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.7 Single Socket Holding Force |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.4.1.9 Shock                       | <br>· · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9/4.1.2 OR940                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

PCMCIA @ 1992, 1983

July, 1993

|          |                  |                             |                                                       |                                        | 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - |      |

|----------|------------------|-----------------------------|-------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|

| 3.       | 4.2 Electrical F | Performance                 |                                                       |                                        | *****                                                                                                           |      |

|          | 3.4.2.1 Cor      | tact Resistance (low level  | )                                                     |                                        | ******                                                                                                          |      |

| era el 1 | 3.4.2.2 Will     | hstandable Voitace          |                                                       |                                        | ****                                                                                                            | 3-7  |

|          | 3.4.2.3 inst     | lation Resistance           |                                                       |                                        |                                                                                                                 |      |

| · · ·    | 3.4.2.4 Cur      | rent Capacity               |                                                       |                                        |                                                                                                                 | 3-8  |

|          | 3.4.2.5 Inst     | lation Material             |                                                       |                                        |                                                                                                                 |      |

|          | A 3 Environme    | ntal Performance            |                                                       | ****                                   |                                                                                                                 | 3-8  |

|          | 2 4 2 4 One      | erating Environment         |                                                       | i dati i                               | e de la companya de l |      |

|          | 3 4 7 7 Cin      | rage Environment            |                                                       |                                        |                                                                                                                 | 3-8  |

|          |                  | ntal Resistance             |                                                       |                                        |                                                                                                                 |      |

| 3.       |                  |                             |                                                       |                                        |                                                                                                                 |      |

| •        |                  | sture Resistance            |                                                       |                                        |                                                                                                                 |      |

|          | 3.4.4.2 The      | rmal Shock,                 |                                                       | ************                           |                                                                                                                 |      |

|          | 3.4.4.3 Dur      | ability (High Temperature)  | *****                                                 | ******                                 |                                                                                                                 |      |

|          |                  | d Resistance                |                                                       |                                        |                                                                                                                 |      |

|          | 3.4.4.5 Hur      | nidity (Normal Condition)   |                                                       |                                        |                                                                                                                 |      |

|          | 3.4.4.6 Hyc      | Irogen Sulfide              |                                                       | •••••••••••••••••••••••••••••••••••••• |                                                                                                                 |      |

| · . · ·  |                  | Water Spray                 |                                                       |                                        |                                                                                                                 |      |

| 3.5 Ce   | nnector Du       | rability                    |                                                       | ************************************   |                                                                                                                 |      |

|          |                  | ironment                    |                                                       |                                        |                                                                                                                 |      |

|          |                  |                             |                                                       |                                        |                                                                                                                 |      |

|          |                  | ironment                    |                                                       |                                        |                                                                                                                 |      |

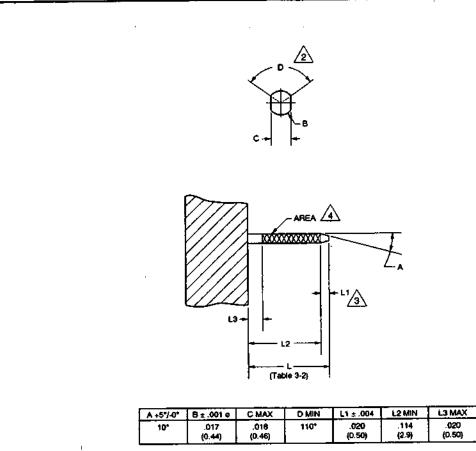

| 3.6 PC   | Card Envir       | onmentai                    | 1 1 - cus upf&&R1++44++++++++++++++++++++++++++++++++ | F444+8424442888F5+8424448844784999     |                                                                                                                 | 3-10 |

|          |                  | ntal Performance            |                                                       |                                        |                                                                                                                 |      |

| 0.       |                  | arating Environment         |                                                       |                                        |                                                                                                                 | 3.10 |

|          | 3.6.1.1 Opt      | rage Environment            |                                                       |                                        |                                                                                                                 | 3.10 |

|          |                  |                             |                                                       |                                        |                                                                                                                 |      |

| 3.       | 6:2 Environma    | ntal Resistance             |                                                       |                                        |                                                                                                                 |      |

|          |                  | h Storage Temperature       |                                                       |                                        |                                                                                                                 |      |

|          |                  | Storage Temperature         |                                                       |                                        |                                                                                                                 |      |

|          |                  | h Operating Temperature.    |                                                       |                                        |                                                                                                                 |      |

| ÷        |                  | Operating Temperature       |                                                       |                                        |                                                                                                                 |      |

|          | 3.6.2.5 The      | mal Shock                   |                                                       |                                        |                                                                                                                 | 3-11 |

|          |                  | slure Resistance            |                                                       |                                        |                                                                                                                 |      |

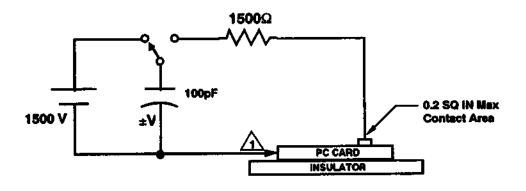

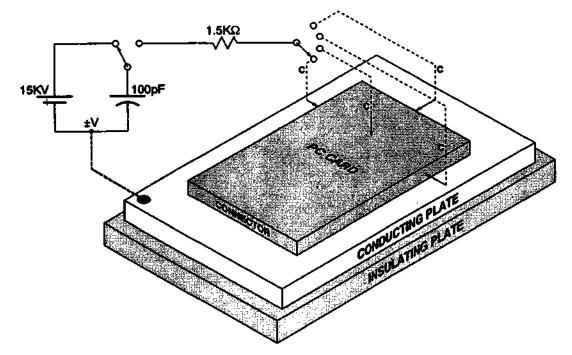

|          |                  | ctrostatic Discharge        |                                                       |                                        |                                                                                                                 |      |

|          |                  | y Exposure                  |                                                       |                                        |                                                                                                                 |      |

|          | 3.6.2.9 UKr      | aviolet Light Exposure      | · · · · · · · · · · · · · · · · · · ·                 |                                        | *******                                                                                                         |      |

|          | 3.6.2.10 EM      | ectromagnetic Field Interfe | rence                                                 |                                        |                                                                                                                 | 3-12 |

|          |                  | rd inverse insertion        |                                                       |                                        | 7                                                                                                               |      |

|          |                  | bration and High Frequenc   |                                                       |                                        |                                                                                                                 |      |

|          |                  | 10ck                        |                                                       |                                        |                                                                                                                 |      |

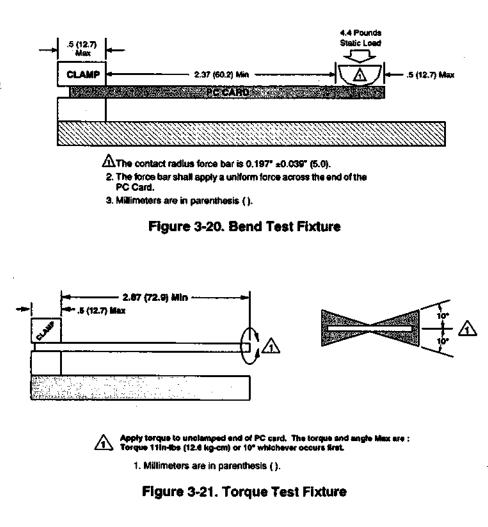

| di Anna  |                  | nd Test                     |                                                       |                                        |                                                                                                                 |      |

|          |                  | op Test                     |                                                       |                                        |                                                                                                                 |      |

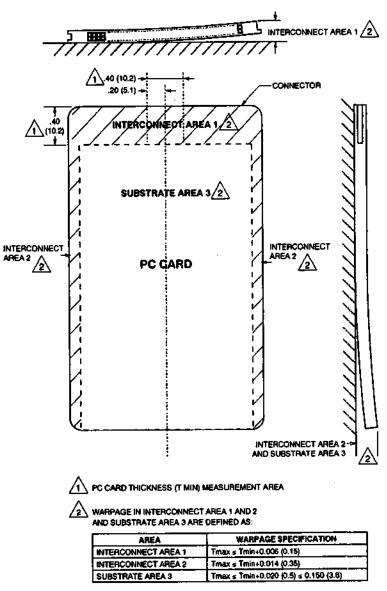

|          |                  | rque Test                   |                                                       |                                        |                                                                                                                 |      |

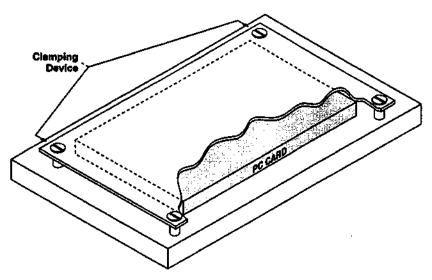

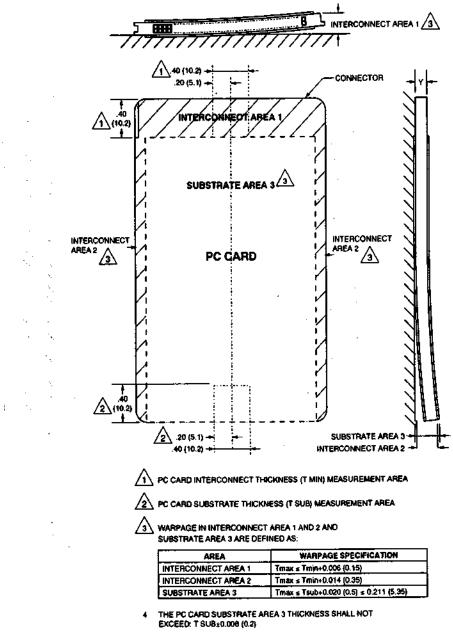

|          |                  | Card Warpage                |                                                       |                                        |                                                                                                                 |      |

|          | 3.6.2.18 SF      | AM Data Retention           |                                                       |                                        | · · · · · · · · · · · · · · · · · · ·                                                                           | 3-14 |

## **4. CARD INTERFACE**

ii 🛛

| 4.1 Pin Assignments                  | ********                              | *********    | <br>    |

|--------------------------------------|---------------------------------------|--------------|---------|

| 4.2 Memory Card Features             | • • • • • • • • • • • • • • • • • • • | ~~~~******** | <br>4-4 |

| 4.2.1 Memory Types and Speed Version |                                       |              |         |

| 4.2.2 Memory Address Space           |                                       |              | <br>    |

| 4.2.3 Memory Only Interface          |                                       |              |         |

| 4 2.4 I/O Address Space              |                                       |              | <br>    |

| 4.2.5 I/O Interface                  |                                       |              |         |

July, 1993

PCMCIA @ 1992, 1993

1915

|                                                       | the fact area and a second and         |                   | and the second |                                                                                                                  | 64A - 302 M - 177 |

|-------------------------------------------------------|----------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|

| 4.2.6 Custom Interfaces                               |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.2.6 Custom Interfaces<br>4.2.7 Configurable Cards   |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.2.7 Compatibility Between I                         |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

|                                                       |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3 Signal Description                                | ******                                 |                   | ***************************************                                                                          | *****                                                                                                            |                   |

| 4.3.1 Address BUS (A0-A25)                            |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3.2 Data BUS (D0-D15)                               |                                        |                   |                                                                                                                  | ·····                                                                                                            |                   |

| 4.3.3 Card Enable (-CE1 & -C                          | )E2)                                   |                   | •                                                                                                                |                                                                                                                  |                   |

| 4.3.4 Output Enable (-OE)                             |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3.5 Write Enable/Program (                          |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3.6 Ready/Busy (+RDY/-BS                            |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

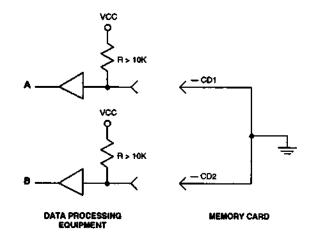

| 4:3:7 Card Detect (-CD1 & -C                          | :D2)                                   |                   |                                                                                                                  | ·····                                                                                                            |                   |

| 4.3.8 Write Protect (+WP)                             | ·                                      |                   | ·····                                                                                                            |                                                                                                                  |                   |

| 4.3.9 Attribute Memory Select                         | t (-REG)                               |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3.10 Battery Voltage Detect                         | (6VO1 & 8VD)                           | 2)                |                                                                                                                  |                                                                                                                  |                   |

| 4.3.11 Program and Peripher                           | al Voltages (Vp                        | p1 & Vpp2)        |                                                                                                                  |                                                                                                                  |                   |

| 4.3.12 Card Voltage and Gro                           | und (Vcc & GNI                         | D)                |                                                                                                                  |                                                                                                                  |                   |

| 4.3.13 Refresh (RFSH)                                 |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.3.14 Reserved Pins (RFU).                           |                                        |                   |                                                                                                                  |                                                                                                                  | 4-13              |

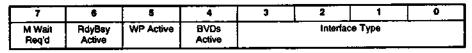

| 4.4 Release 2 Signals Affecti                         | ng Both Men                            | ory Only and I/O  | Interfaces                                                                                                       |                                                                                                                  |                   |

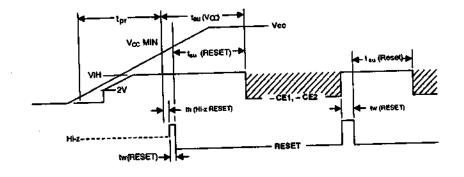

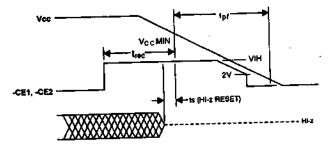

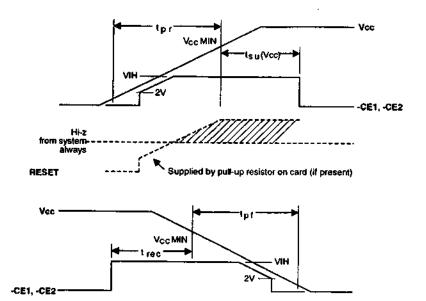

| 4.4.1 Card Reset (RESET)                              | · · ·                                  |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.4.2 Extend Bus Cycle (-WA                           |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

|                                                       | -                                      |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.5 I/O Interface Signals Rep                         |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

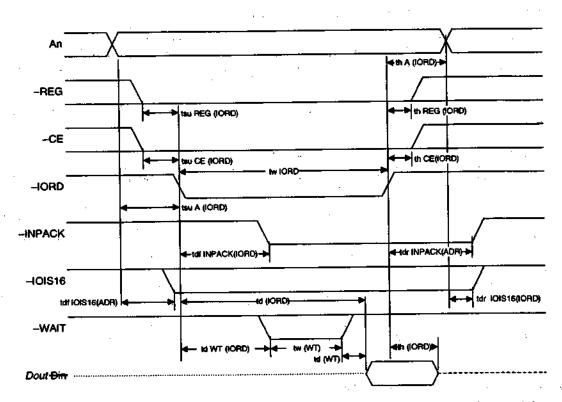

| 4.5.1 I/O Read (-IORD)                                |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

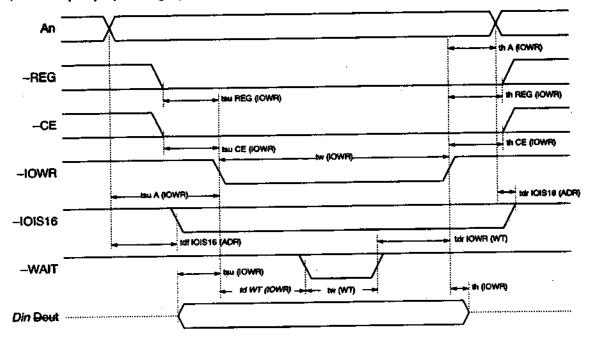

| 4.5.2 I/O Write (-IOWR)                               | ······                                 |                   | ner en                                                                       |                                                                                                                  |                   |

| 4.5.3 Input Acknowledge (-IN                          |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.6 I/O Interface Signals Repl                        | lacing Memo                            | ry Interface Sign | als                                                                                                              | *********                                                                                                        |                   |

| 4.6.1 1/O IS 16 Bit Port (-1015                       | 16) [replaces W                        | /P]               | ······································                                                                           |                                                                                                                  |                   |

| 4.6.2 interrupt Request (-IRE                         | Q) (replaces +R                        | DY/-BSY]          |                                                                                                                  |                                                                                                                  |                   |

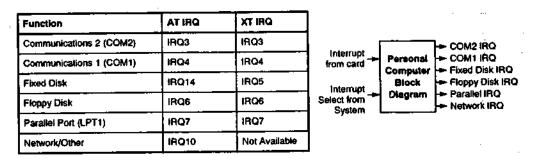

| 4.6.2.1 Interrupt Reques                              | t Routing                              |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.6.2.2 Pulsed- and Leve                              |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.6.2.3 Pulsed Mode Inte                              | · · · · - ·                            |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.6.2.4 Level-Mode Inter<br>4.6.2.5 Interrupts and +F |                                        |                   | •                                                                                                                | and the second |                   |

| 4.6.3 Audio Digital Waveform                          |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.6.4 Status Changed (-STSC                           |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

|                                                       | 1111 111 11 11 11 11 11 11 11 11 11 11 | a second second   |                                                                                                                  |                                                                                                                  |                   |

| 4.7 Operating Conditions                              |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.7.1 Default Conditions and (                        |                                        | •                 |                                                                                                                  |                                                                                                                  |                   |

| 4.8 Memory Function                                   |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.1 Common Memory Funct                             |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.2 Common Memory Read                              |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.3 Common Memory Write                             |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.4 Common Memory Write                             |                                        |                   | •                                                                                                                | · .                                                                                                              |                   |

| 4.8.5 Attribute Memory Functi                         |                                        | -                 |                                                                                                                  |                                                                                                                  |                   |

| 4.8.6 Attribute Memory Read I                         |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.7 Attribute Memory Write I                        |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

| 4.8.8 Attribute Memory Write I                        |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

|                                                       |                                        |                   | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                           |                                                                                                                  |                   |

| 4.8.9 Write Protect Function                          |                                        |                   |                                                                                                                  |                                                                                                                  |                   |

PCMCIA @ 1992, 1993

July, 1993

iii

|                                                 | 4.9.1 Common Memory Timing Specification                    |                                                                                                                                                                                                                                    |                                          | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                              | ,      |

|-------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

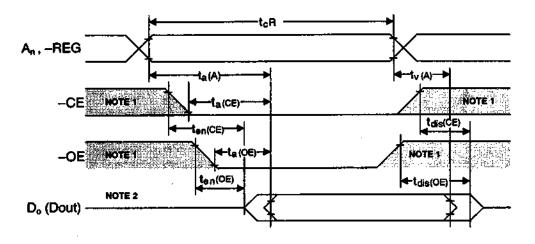

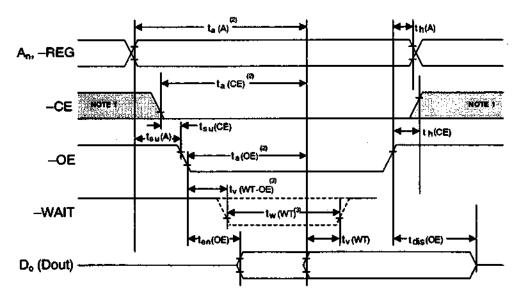

|                                                 | 4.9.2 Common Memory Read Timing for all types               | s of Memory                                                                                                                                                                                                                        |                                          |                                                                                                                                                                                                                                    | 4-19   |

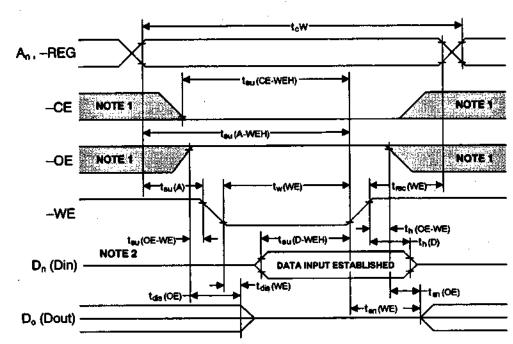

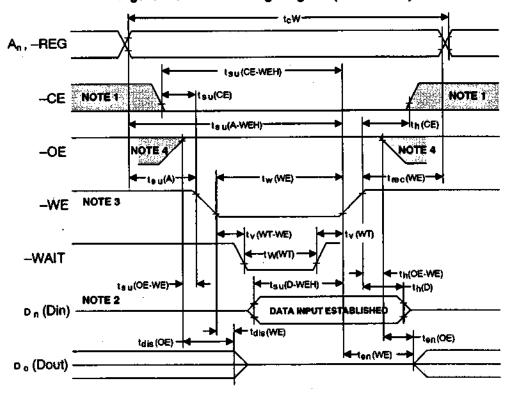

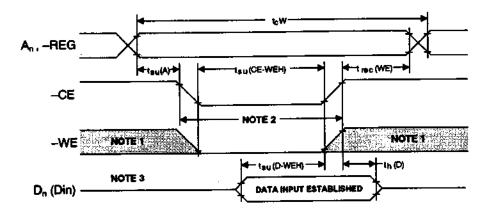

|                                                 | 4.9.3 Write Timing for SRAM Card                            |                                                                                                                                                                                                                                    |                                          |                                                                                                                                                                                                                                    | 4-20   |