| UNITED STA | ATES PATENT AND TRADEMARK OFFICE                          |

|------------|-----------------------------------------------------------|

| BEFORE TH  | HE PATENT TRIAL AND APPEAL BOARD                          |

|            | Intel Corporation, Petitioner,                            |

|            | v.                                                        |

|            | Qualcomm Incorporated, Patent Owner                       |

|            | Case IPR2018-01334 <sup>1</sup> U.S. Patent No. 8,838,949 |

## PATENT OWNER SUR-REPLY

<sup>&</sup>lt;sup>1</sup> IPR2018-01335 and IPR2018-01336 have been consolidated with the instant proceeding.

## **Table of Contents**

| I.   | Introduction                     |                                                                                                                                                                           |    |

|------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| II.  | Claim Construction               |                                                                                                                                                                           |    |

|      | A.                               | "System Memory"                                                                                                                                                           | 2  |

|      |                                  | 1. Petitioner's Construction is Unclear                                                                                                                                   |    |

|      |                                  | 2. A Construction That Defines "System Memory" Based on the Data That is Loaded Into the Memory is Erroneous and Does Not Reflect Any Characteristic of the Memory Itself | 3  |

|      | B.                               | "Image Header"                                                                                                                                                            | 10 |

|      | C.                               | "Hardware Buffer"                                                                                                                                                         | 11 |

|      | D.                               | "Scatter Loader Controller"                                                                                                                                               | 13 |

|      | E.                               | Means-Plus-Function Limitations                                                                                                                                           | 14 |

| III. | Claims 1-23 Are Not Unpatentable |                                                                                                                                                                           | 15 |

|      | A.                               | Petitioner's Reliance on "Bauer and Svensson Combined" is Inconsistent With the Proper Obviousness Inquiry Mandated by <i>Graham</i>                                      | 15 |

|      | B.                               | Qualcomm Acknowledges That Bauer and Svensson Could Be Combined, and Petitioner's Repeated Argument on this Point is a Red Herring                                        | 16 |

|      | C.                               | Bauer and Svensson Combined Fail to Disclose Loading Each Received Data Segment Directly to System Memory of the Secondary Processor.                                     | 17 |

|      | D.                               | Petitioner Failed to Prove That It Would Have Been Obvious to Transfer an Image in Bauer's File Format to a Secondary Processor                                           | 26 |

|      | E.                               | Bauer and Svensson Combined Fail to Meet the "Scatter Loading" Limitations                                                                                                | 29 |

|      | F.                               | The Cited References Fail to Disclose a Secondary Processor<br>Receiving an Image Header and Each Data Segment Separately                                                 | 31 |

|      | G.                               | Bauer and Svensson Fail to Meet the Claimed "Hardware Buffer"                                                                                                             | 35 |

| IV | Conclusion | 24         |

|----|------------|------------|

| ıν | Conclusion | <b>)</b> [ |

## I. Introduction

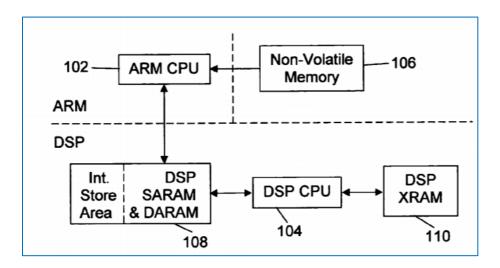

Petitioner's reply introduces unpersuasive arguments that cannot salvage the petitions. The thrust of Petitioner's unpatentability argument is that the intermediate storage area of Bauer/Svensson is not "system memory," and therefore data is loaded "directly" to the DSP XRAM (*i.e.*, the alleged "system memory") despite the data being temporarily buffered in the intermediate storage area. *See*, *e.g.*, Paper 21 at 34-35.

Ex. 1010 (Svensson) at Fig. 1.

But this is erroneous because the intermediate storage area of Bauer/Svensson is indistinguishable from the temporary buffer in system memory that is described in the Background section of the '949 patent. Ex. 1001 at 2:14-41. Both are temporary buffers that are *allocated at run time* and used to hold data that is subsequently transferred to a final destination in system memory:

Ex. 1001 ('949 Background) at 2:23-34: "[O]ne way of performing such loading is to allocate a temporary buffer .... From the temporary buffer, ... the payload would get copied over to the final destination [in system memory]. The temporary buffer would be some place in system memory."

Ex. 1010 (Svensson) at 5:21-28: "The idle process reserves a block of memory in the slave's heap of memory ... [in] 'internal' memory 108 (Step 212). ... [T]his reserved block of memory is used for intermediate storage of information (code and/or data) to be transferred to the ... 'external' XRAM 110."

See Section III.C below. The combination of Bauer and Svensson thus describes the prior-art temporary buffering operation that the invention of the '949 patent seeks to avoid, and therefore *does not* disclose loading data segments directly to system memory, as required by all of the challenged claims.

The Board should confirm the patentability of claims 1-23 for this reason and those explained below.

## II. Claim Construction

## A. "System Memory"

Qualcomm showed in its response that the claim term "system memory" should be interpreted to mean "memory that is addressable by the secondary processor." Paper 16 at 9-12. On reply, Petitioner disagrees and argues that the term should be construed as "memory where an executable software image can be loaded and executed." Paper 21 at 6. The Board should reject Petitioner's construction and adopt Qualcomm's for the reasons explained below. But even if the Board were to

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

# **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

# **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.