US006904484B1

# (12) United States Patent Nelson

## (10) Patent No.: US 6,904,484 B1 (45) Date of Patent: Jun. 7, 2005

| (54) | LOW PIN COUNT (LPC) FIRMWARE HUB |

|------|----------------------------------|

|      | RECOVERY                         |

| (75) | Inventor: | Albert   | Rudy | Nelson, | Olympia, | WA |

|------|-----------|----------|------|---------|----------|----|

|      |           | (T.T.C.) |      |         |          |    |

(US)

(73) Assignee: Intel Corporation, Santa Clara, CA

(US)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by **● d**ays.

| (21) | Appl. | No.: | 09/539,517 |

|------|-------|------|------------|

|------|-------|------|------------|

| (22) File | ed: N | Iar. 30, | 2000 |

|-----------|-------|----------|------|

|-----------|-------|----------|------|

| 13/00 |

|-------|

|       |

185.33

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

5,600,801 A \* 2/1997 Parks et al. ...... 710/104

| 5,784,611    | Α          | * | 7/1998  | Thantrakul 713/1               |

|--------------|------------|---|---------|--------------------------------|

| 6,188,6●2    | B1         | * | 2/2001  | Alexander et al 365/185.04     |

| 6,291,976    | B1         | * | 9/2001  | Kaminski et al 323/283         |

| 6,442,●67    | B1         | * | 8/2002  | Chawla et al 365/185.08        |

| 2001/0018721 | <b>A</b> 1 | * | 8/2001  | McKenna et al 71 <b>0</b> /126 |

| 2002/0184297 | <b>A</b> 1 | * | 12/2002 | Krancher et al 709/201         |

| 2003/0023761 | <b>A</b> 1 | * | 1/2003  | Jeansonne et al 709/250        |

<sup>\*</sup> cited by examiner

Primary Examiner—Rupal Dharia (74) Attorney, Agent, or Firm—Paul E. Steiner

#### (57) ABSTRACT

A method and apparatus for low pin count firmware hub recovery on a circuit board having a firmware hub includes coupling a firmware hub recovery module having a firmware program onto the circuit board, establishing communication between a central processing unit (CPU) and the firmware hub recovery module, and reprogramming the firmware hub by the firmware program.

#### 22 Claims, 3 Drawing Sheets

Jun. 7, 2005

FIG. 1

FIG. 2

FIG. 3

1

#### LOW PIN COUNT (LPC) FIRMWARE HUB RECOVERY

#### FIELD OF THE INVENTION

Embodiments of the present invention provide a method and apparatus for firmware hub programming on a circuit board. More particularly, embodiments of the present invention provide methods and apparatus for low pin count (LPC) firmware hub recovery on a circuit board via a firmware hub recovery module.

#### BACKGROUND OF THE INVENTION

Conventional computer systems include a variety of 15 peripheral and memory devices that communicate with the systems's central processing unit (CPU) or chip-set processor via an Industry Standard Architecture (ISA) bus or an Expansion bus (X-bus). The CPU or chip-set processor includes a large amount of pins (e.g., approximately 50-70) 20 and associated circuitry to support the ISA bus or X-bus signals that are used to interface the CPU or chip-set processor with the peripheral devices including input/output (I/O) or I/O controllers, floppy disk controller, keyboard controllers, and memory devices such as non-volatile 25 memory devices that store, for example basis input-output system (BIOS) information.

The large number of pins needed to support the ISA bus and X-bus standards generally increase the overall system cost. For example, larger packages are required for a CPU or chip-set. The development of the low pin count (LPC) bus has obviated to some extent the problem mentioned above. The LPC bus includes general purpose signal lines that carry substantially all time-multiplexed address, data and control information to implement memory, I/O, and bus transactions 35 between the CPU and other system devices.

Presently there are no other peripheral components that are connected to the LPC bus because the LPC bus is designed to be a "local bus" servicing the chip-set. The LPC bus does not provide for expandability for add-on features like that provided for by a Peripheral Component Interconnect (PCI) (e.g., PCI Local Bus Specification, version 2.1, a copy of which may be obtained from the PCI Special Interest Group) bus for example. In general the LPC bus may be limited to being coupled to a system bus interface controller and one or more memory devices. As used herein, the term "firmware hub" refers to the memory devices coupled to a LPC bus.

The firmware in the firmware hub is a computer program including a series of instructions or statements arranged in a specific sequence and written in a language executable by the processor of the computing device to achieve a certain result.

Firmware, as used herein, refers to those computer programs whose instructions and/or data are stored and maintained permanently in the computing device without the need for the continued application of power. One such computer program is the basic input/output system (BIOS). These computer programs, like the BIOS are typically stored in non-volatile read only memory (ROM), programmable read only memory (PROM) or erasable programmable read only memory (EPROM). Use of a non-volatile memory obviates the need to reload the programming into the computing device in the event of a power loss or turn-off.

2

when programming corrections or upgrades are required. The EEPROM includes a read only memory device whose individual data storage locations (addresses) are erasable and can be reprogrammed by applying certain electrical signals to the chip. New firmware can thus be stored in the chip without removing the chip from the computing device. However, in situations where the computing device's firmware has been corrupted to an extent that the computing device is unable to boot-up, the above mentioned method of supplying new firmware is not available. In these cases, there is no other solution but to replace the firmware chip.

In view of the foregoing, it can be appreciated that a substantial need exists for a method and apparatus for low pin count firmware hub recovery.

#### BRIEF DESCRIPTION OF THE DRAWINGS

The features and advantages of the present invention will become apparent from the following detailed description in combination with the figures listed below.

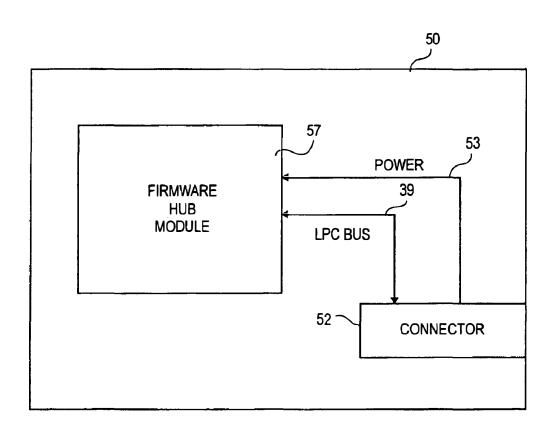

FIG. 1 is a block diagram of an circuit board including a low pin count (LPC) bus according to an embodiment of the present invention.

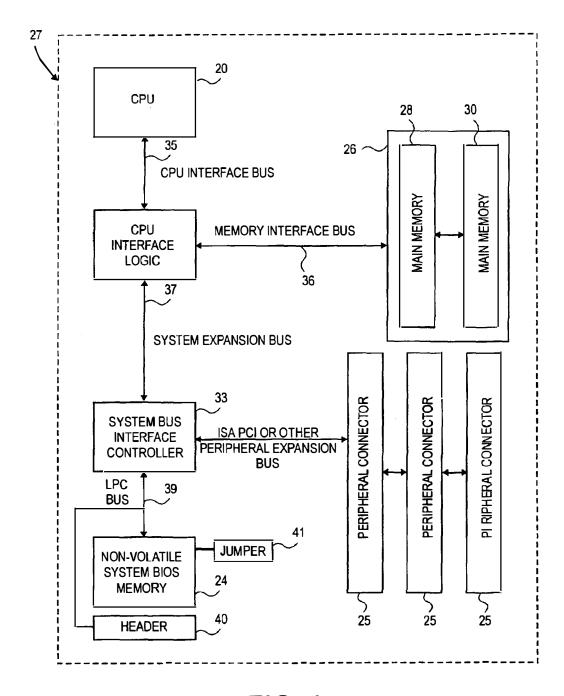

FIG. 2 is a block diagram of a firmware hub updating module according to an embodiment of the present invention.

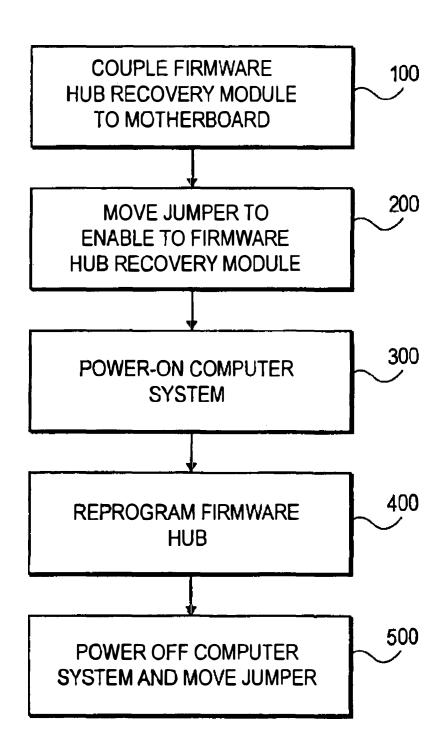

FIG. 3 is a flow diagram illustrating a method for low pin count (LPC) firmware hub recovery in accordance with an embodiment of the present invention.

#### DETAILED DESCRIPTION

Embodiments of methods and systems for low pin count (LPC) firmware hub recovery using a firmware hub recovery module

In the following description, for purposes of explanation, numerous specific details are set forth to provide a thorough understanding of the present invention. It will be appreciated, however, by one skilled in the art that the present invention may be practiced without these specific details. In other instances, structures and devices are shown in block diagram form. Furthermore, one skilled in the art can readily appreciated that the specific sequence in which methods are presented and performed are illustrative and it is contemplated that the sequences can be varied and still remain within the spirit and scope of the present invention.

FIG. 1 illustrates a block diagram of a computer system's circuit board 27 including a low pin count (LPC) bus 39 according to an embodiment of the present invention. Circuit board 27 may be a mother board and typically includes a processor such as a central processing unit or CPU 20. The CPU is the "brains" or "engine" of the computer system responsible for overseeing all execution of operations in the computer. Motherboard 27 also includes CPU interface logic 21, coupled to CPU 20 and interfacing CPU 20 with other circuit components such as a system bus interface controller 33 and main memory 26. As shown, system bus interface controller 33 may be any type of expansion bus controller such as a PCI bus or peripheral bus I/O controller. System bus interface controller 33 is coupled to CPU interface logic 21 and is coupled to peripheral connectors 25 via expansion bus 38. A bus that complies with a Peripheral Component Interconnect (PCT) standard (e.g., PCI Local Bus Specification, version 2.1, a copy of which may be obtained from the PCI Special Interest Group) is a example of such 65 an expansion bus. Main memory 26 may include random

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

### **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

### **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

#### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

#### **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.