US011061682B2

# (12) United States Patent

#### Vorbach

#### (54) ADVANCED PROCESSOR ARCHITECTURE

(71) Applicants: Martin Vorbach, Lingenfeld (DE);

Hyperion Core, Inc., Los Gatos, CA

(US)

(72) Inventor: Martin Vorbach, Lingenfeld (DE)

(\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35

U.S.C. 154(b) by 0 days.

(21) Appl. No.: 15/535,697

(22) PCT Filed: Dec. 13, 2015

(86) PCT No.: **PCT/US2015/065418**

§ 371 (c)(1),

(65)

(2) Date: Jun. 13, 2017

(87) PCT Pub. No.: **WO2016/100142**

PCT Pub. Date: Jun. 23, 2016

US 2018/0004530 A1 Jan. 4, 2018

#### (30) Foreign Application Priority Data

| Dec. 15, 2014 | (EP) | <br>14197929  |

|---------------|------|---------------|

| Jun. 24, 2015 | (EP) | <br>150201036 |

**Prior Publication Data**

(51) Int. Cl. G06F 9/38 (2018.01) G06F 9/30 (2018.01) G06F 9/32 (2018.01)

(52) **U.S. Cl.**CPC ............. *G06F 9/3855* (2013.01); *G06F 9/3001* (2013.01); *G06F 9/3017* (2013.01); (Continued)

(58) Field of Classification Search

### (10) Patent No.: US 11,061,682 B2

(45) **Date of Patent:**

Jul. 13, 2021

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(Continued)

#### FOREIGN PATENT DOCUMENTS

EP 14185745.8 9/2014 WO 2002/071249 9/2002 (Continued)

#### OTHER PUBLICATIONS

Cheol-Ho Jeong, Woo-Chan Park, Tack-Don Han, Sang-Woo Kim and Moon-Key Lee, "In order issue out-of-order execution floating-point coprocessor for CalmRISC32," Proceedings 15th IEEE Symposium on Computer Arithmetic. ARITH-15 2001, Vail, CO, USA, 2001, pp. 195-200, doi: 10.1109/ARITH.2001.930119.\*

(Continued)

Primary Examiner — Michael J Metzger (74) Attorney, Agent, or Firm — IP Spring

#### (57) ABSTRACT

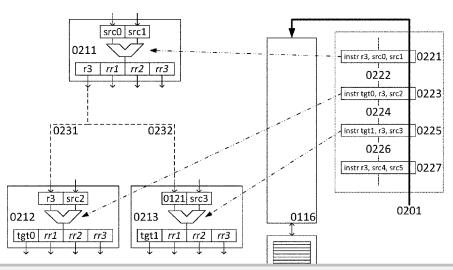

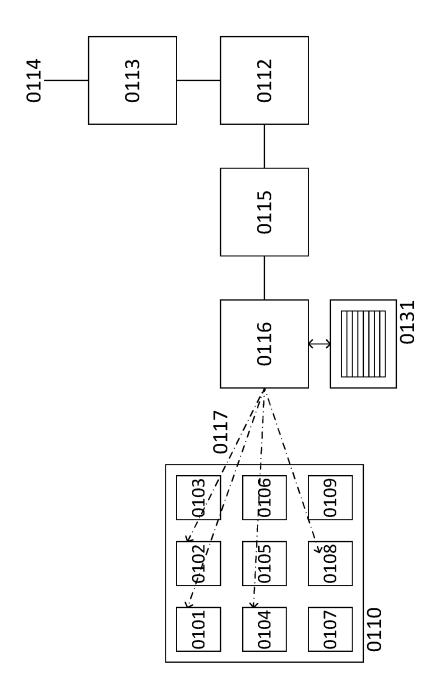

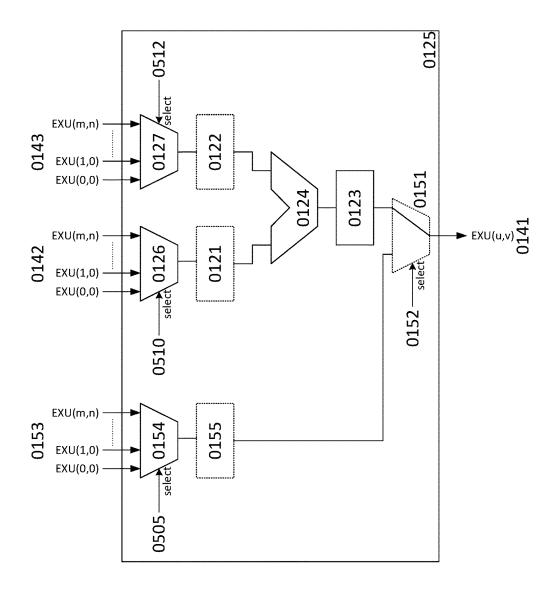

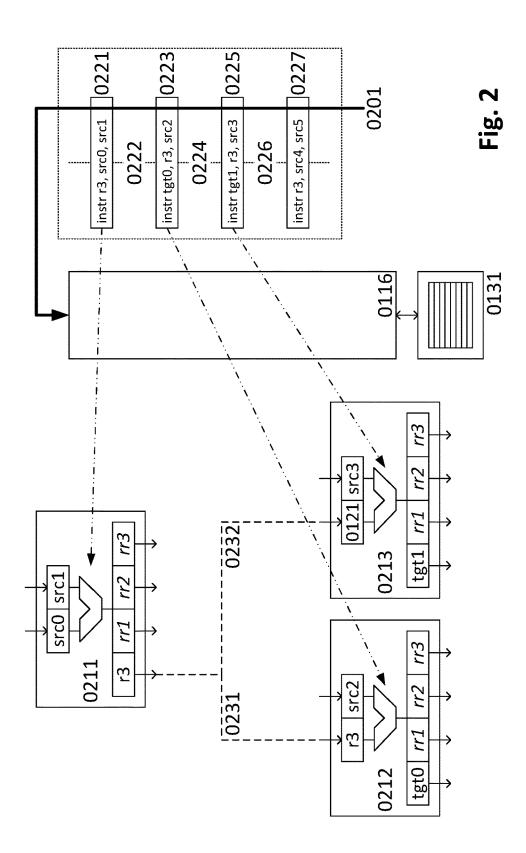

The invention relates to a method for processing instructions out-of-order on a processor comprising an arrangement of execution units. The inventive method comprises looking up operand sources in a Register Positioning Table and setting operand input references of the instruction to be issued accordingly, checking for an Execution Unit (EXU) available for receiving a new instruction, and issuing the instruction to the available Execution Unit and entering a reference of the result register addressed by the instruction to be issued to the Execution Unit into the Register Positioning Table (RPT).

#### 20 Claims, 26 Drawing Sheets

(52) U.S. CI.

CPC ...... G06F 9/30065 (2013.01); G06F 9/30098

(2013.01); G06F 9/325 (2013.01); G06F

9/327 (2013.01); G06F 9/382 (2013.01);

G06F 9/384 (2013.01); G06F 9/3824

(2013.01); G06F 9/3826 (2013.01); G06F

9/3828 (2013.01); G06F 9/3836 (2013.01);

G06F 9/3842 (2013.01); G06F 9/3846 (2013.01); G06F

9/3848 (2013.01); G06F 9/3857 (2013.01);

G06F 9/3848 (2013.01); G06F 9/3857 (2013.01);

G06F 9/3861 (2013.01); G06F 9/3863

#### (56) References Cited

#### U.S. PATENT DOCUMENTS

(2013.01); G06F 9/3885 (2013.01)

| 7,096,345    | B1* | 8/2006 | Chen G06F 9/3838                 |

|--------------|-----|--------|----------------------------------|

| 7,111,152    | B1* | 9/2006 | 712/217<br>Cofler G06F 9/3836    |

|              |     |        | 712/216<br>Sugimoto G06F 9/30083 |

|              |     |        | 712/215                          |

| 2007/0055852 | A1* | 3/2007 | Hanes G06F 9/3851                |

| 2013/0205123 | A1* | 8/2013 | Vorbach G06F 9/30043             |

|              |     |        | 712/221                          |

#### FOREIGN PATENT DOCUMENTS

| WO | 2010/142432 | 2/2010  |

|----|-------------|---------|

| WO | 2010/043401 | 4/2010  |

| WO | 2011/079942 | 7/2011  |

| WO | 2012/003997 | 1/2012  |

| WO | 2012/123061 | 9/2012  |

| WO | 2012/167933 | 12/2012 |

| WO | 2013/098643 | 7/2013  |

#### OTHER PUBLICATIONS

"ARM7TDMI-S Data Sheet", Document No. ARM DDI 0084D, ARM Ltd., UK, 1998, 60 pages.

Balasubramonian, "Lecutre Notes: Out-of-Order Processors", University of Utah, Oct. 13, 2007, 8 pages.

European Patent Office, International Search Report for International Patent Application No. PCT/US2015/065418, dated Jul. 7, 2016, 6 pages.

European Patent Office, Written Opinion for International Patent Application No. PCT/US2015/065418, dated Jul. 7, 2016, 8 pages. Fog, "The microarchitecture of Intel, AMD and VIA CPUs: An optimization guide for assembly programmers and compiler makers", http://www.agner.org/optimize/microarchitecture.pdf, 1996-2017, 233 pages.

Goulding-Hotta, et al., "The GreenDroid Mobile Application Processor: an Architecture for Silicon's Dark Future", University California, San Diego; Published by the IEEE Computer Society, Mar./Apr. 2011, 10 pages.

Gunadi, et al., "CRIB: Consolidated Rename, Issue, and Bypass", ISCA'11, Jun. 4-8, 2011, San Jose, California, USA, 2011, 10 pages.

Rotenberg, et al., "Trace Cache: a Low Latency Approach to High Bandwith Instruction Fetching", Proceedings of the 29th annual ACM/IEEE international symposium on Microarchitecture. IEEE Computer Society, 1996, 12 pages.

Thomadakis, "The Architecture of the Nehalem Processor and Nehalem-EP SMP Platforms", Texas A&M University, Mar. 17, 2011, 49 pages.

Tomasulo, "An Efficient Algorithm for Exploiting Multiple Arithmetic Units", IBM Journal of Research and Development archive; vol. 11, Issue 1, Jan. 1967, pp. 25-33.

UK Intellectual Property Office, Examination Report for United Kingdom Patent Application No. 1711202.0, dated Aug. 20, 2018, 5 pages.

UK Intellectual Property Office, Examination Report for United Kingdom Patent Application No. 1711202.0, dated Aug. 17, 2017, 10 pages.

"Computer Organization and Architecture, Chapter 15. Control Unit Operation", umcs.maine.edu, http://aturing.umcs.maine.edu/~meadow/courses/cos335/COA15.pdf, Mar. 16, 2010, 9 pages.

Lazzaro, "CS 152 Computer Architecture and Engineering: Lecture 6—Superpipelining + Branch Pre-diction", UC Berkeley, https://inst.eecs.berkeley.edu/~cs152/sp14/lecnotes/lec3-2.pdf, Feb. 6, 2014, 37 pages.

Sima, Dezso "Microarchitecture of Superscalars (3): Branch Prediction", Universitas Budensis, John von Neumann Faculty of Informatics, Fall 2007, 73 pages.

\* cited by examiner

Fig. 1

ig. 1A

# DOCKET

# Explore Litigation Insights

Docket Alarm provides insights to develop a more informed litigation strategy and the peace of mind of knowing you're on top of things.

## **Real-Time Litigation Alerts**

Keep your litigation team up-to-date with **real-time** alerts and advanced team management tools built for the enterprise, all while greatly reducing PACER spend.

Our comprehensive service means we can handle Federal, State, and Administrative courts across the country.

## **Advanced Docket Research**

With over 230 million records, Docket Alarm's cloud-native docket research platform finds what other services can't. Coverage includes Federal, State, plus PTAB, TTAB, ITC and NLRB decisions, all in one place.

Identify arguments that have been successful in the past with full text, pinpoint searching. Link to case law cited within any court document via Fastcase.

## **Analytics At Your Fingertips**

Learn what happened the last time a particular judge, opposing counsel or company faced cases similar to yours.

Advanced out-of-the-box PTAB and TTAB analytics are always at your fingertips.

### API

Docket Alarm offers a powerful API (application programming interface) to developers that want to integrate case filings into their apps.

#### **LAW FIRMS**

Build custom dashboards for your attorneys and clients with live data direct from the court.

Automate many repetitive legal tasks like conflict checks, document management, and marketing.

#### **FINANCIAL INSTITUTIONS**

Litigation and bankruptcy checks for companies and debtors.

## **E-DISCOVERY AND LEGAL VENDORS**

Sync your system to PACER to automate legal marketing.